Микропроцессорлық жүйелер: құрылым принциптері, жұмыс режимдері, Intel 8085 және микроконтроллерлер

ҚАЗАҚСТАН РЕСПУБЛИКАСЫНЫҢ БІЛІМ ЖӘНЕ ҒЫЛЫМ МИНИСТРЛІГІ

“Алматы энергетика және байланыс институты”

коммерциялық емес акционерлік қоғамы

О. Т. Шанаев

МИКРОПРОЦЕССОРЛЫҚ ЖҮЙЕЛЕР

Оқу құралы

Алматы 2009

Оқу құралында жеке микропроцесорлар мен микропроцессорлық жинам микросхемаларының негізіндегі дәстүрлі микропроцессорлық жүйелердің құрама бөліктері, олардың құрылым принциптері және жүйе жұмысының ұйымдастырылу тәртібі қарастырылады. Микропроцессорлардың негізгі құрылым принциптері мен жұмыс тәртібін түсіндіру ыңғайлылығы үшін нақтылы Intel 8085 микропроцессоры алынып, оның ішкі құрама блоктары мен оның іс-әрекетін басқарушы бағдарламаларының құрылу негіздері қарастырылады.

Оқу құралында берілген материалдарды оқып, игеру арқылы студенттердің микропроцессорлық жүйелердің құрылым принциптері және олардың жұмыс тәртібі жөніндегі білімі қалыптастырылып, олардың оқу барысының келесі кезеңдерінде оқылатын арнайы пәндерді игеруіне немесе өздік жұмыс арқылы білім деңгейін көтеруіне қажетті түпнегіз қаланады.

Кіріспе

Микропроцессорлық жүйе (МПЖ) - есептеу, бақылау-өлшеу және басқару жұмыстарын атқаруға арналған, микропроцессор негізіндегі электрондық құрылымдардың жалпылама аталымы. Олардың кіріс және шығыс сигналдары ретінде аналогты сигналдар, жеке цифрлық сигналдар, цифрлық кодтар, цифрлық кодтардың тізбелері пайдаланалуы мүмкін. Микропроцессорлық жүйелерде информацияның өңделуі және сақталуы цифрлық түрде жүргізілетіндіктен, оларға түсетін аналогты кіріс сигналдары аналогты-цифрлы түрлендіргіштер (АЦТ) арқылы таңдалым кодтарының тізбесіне түрлендіріледі, ал олардан өңдеу нәтижесі ретінде шығарылатын аналогты шығыс сигналдары таңдалым кодтарының тізбесінен цифрлы-аналогты түрлендіргіштер (ЦАТ) арқылы қалыптастырылады.

Дәстүрлі цифрлық жүйелердегі информацияның өңделу және сақталу алгоритмдері жүйенің схемақұралысымен ғана анықталады, яғни өзге алгоритмге көшу үшін, оны жүйе құрамындағы электрондық буындардың өзара байланыстарын өзгерту арқылы немесе осы буындарды олардың қойылған мәселеге жарамды түріне ауыстыру арқылы ғана жүзеге асыруға болады немесе жүйенің құрылымын толықтай өзгертуге тура келеді. Әрине, бұндай түрлендірімдердің жүйе жұмысының барысында жүргізілуі мүмкін емес, ол үшін жүйені қайтадан құру керек болады. Тап осы себептен дәстүрлі цифрлық жүйе көбіне “тастай логикалы” жүйе деп аталады.

Кез келген “тастай логикалы” жүйе - алдын ала белгілі жеке бір мәселені (немесе бірнеше жуық мәселелерді) шешуге арналған арнайы жүйе. Оның күмәнсіз артықшылықтары бар.

Біріншіден, арнайы жүйенің құрамында артық элемент болмайды, оның әрбір элементі міндетті түрде толыққанды жұмыс атқарады (әрине, жүйенің дұрыс жобаланғандығында) .

Екіншіден, арнайы жүйеде информацияны өңдеу алгоритмінің орындалу жылдамдығы оның құрамындағы логикалық элементтердің тезәрекеттілігімен және олардың нақтылы байланыстарымен ғана анықталатындықтан, бұндай құрылымдар аса жоғары тезәрекеттілікті қамтамасыз ете алады.

“Тастай логикалы” жүйенің басты кемістігі - әрбір жаңа мәселені шешу үшін оны қайта құру қажеттігінде. Ал бұл - ұзаққа созылатын және қосымша қаражат талап ететін жұмыс.

Бұл кемістіктен құтылу үшін, кез келген мәселеге жеңіл икемделетін жүйе құру керек, яғни, оның шешілетін мәселеге байланысты (құрылымды өзгертпестен) жұмыс алгоритмін (жүйенің жұмыс бағдарламасын) ауыстыру мүмкіншілігі болу керек. Бұндай “икемді логикалы” жүйе әмбебап немесе бағдарламалы жүйеге айналады, микропроцессорлық жүйе тап осындай жүйеге жатады.

Әмбебаптылыққа жету ұтылысқа да әкеледі. Аса күрделі мәселені шешу үшін (қарапайым мәселелермен салыстырғанда) көбірек құрал қажет болады. Сондықтан, әмбебап жүйенің құрамы ең күрделі мәселенің шешілу мүмкіндігін қамтамасыз ету керек. Әрине, қарапайым мәселенің шешілуі кезінде бұндай жүйенің бар мүмкіншілігі толыққанды пайдаланылмайды. Сонымен қатар, әмбаптылық жүйенің (оның құрылымының күрделенуіне байланысты) тезәрекеттілігін де төмендетеді.

Сонымен, келесі қорытындыға келуге болады: “тастай логикалы” жүйелер, аса жоғары тезәрекеттілікті қажет қылатын, өңделу алгоритмдері қарапайым түрдегі, жеке мәселелерге ыңғайлы келеді. Ал әмбебап, бағдарламалы жүйелер, онша тезәрекеттілікті қажет қылмайтын, шешетін мәселелері жиі өзгеріп отыратын және олардың шешілуі күрделі алгоритмдермен жүзеге асырылатын жағдайларға ыңғайлы келеді.

Бірақ соңғы кезде шығарылған әмбебап (микропроцессорлық) жүйелердің тезәрекеттілігі аса (бірнеше дәрежеге) көтерілді және бұндай жүйелерге арналған микросхемалардың шығарылым көлемінің ұлғаюы олардың құнының төмендеуіне әкелді. Оның нәтижесінде “тастай логикалы” жүйелердің қолданылым аймағы тарыла түсті. Бұған қоса, қазіргі заманда ішкі құрылымын бағдарламалы тәсілмен өзгерту арқылы жеке мәселелерді шешуге тез икемделетін микросхемалардың шығарылым технологиясы аса қарқынды дамып келе жатыр. Олар “тастай логикалы” жүйелердің тезәрекеттілігі мен бағдарламалы жүйелердің икемділігін біріктіреді. “Бағдарламалы құрылымдарға” қатысты мәселелер бұл оқу құралында қарастырылмайды.

Оқу құралының бірінші бөлімінде микропроцессорлық жүйелердің құрылым принциптері және олардың құрама бөліктері туралы жалпы түсініктер берілген.

Оқу құралының екінші бөлімінде, жалпы түрде микропроцессорлық жүйе (МПЖ) деп аталатын, есептеу, бақылау-өлшеу және басқару жүйелерінің құрамындағы басты құрылғысы саналатын, микропроцессорлардың құрылымы мен олардың іс-әрекеттерінің ұйымдастырылу тәртібін тиянақты таныстыру мақсатында қарапайым Intel 8085 микропроцессорының ішкі құрылымы мен оның микропроцессорлық жүйенің құрамында қолданылу принциптері және олардың жұмысын басқарушы бағдарламалардың Ассемблер тілінде құрастырылу жолдары қарастырылады.

Оқу құралының үшінші бөлімінде микропроцессорлық жүйенің құрама бөліктері біріктірілген жеке кристалды микроконтроллерлердің құрылым принциптері мен олардың құрамына енгізілетін ерекше буындар қарастырылады.

Оқу құралы автордың өндіріс және педагогика саласындағы көпжылдық тәжірибесінің негізінде жазылды.

1 Микропроцессорлық жүйелер

1. 1 Микропроцессорлық жүйелер жөніндегі жалпы түсініктер

Микропроцессорлық жүйелер (МПЖ) - есептеу, өлшеу-бақылау, басқару жүйелерінде және тұрмыстық техникада кеңінен қолданылатын, микропроцессорлар негізіндегі күрделі электрондық құрылымдардың жалпылама аталымы. Микропроцессорлық жүйелерді құрып, олармен жұмыс істеуді үйрену үшін оларға байланысты басты ұғымдарды түсініп, олардың жалпы құрылым принциптерін, оларды аппаратты және бағдарламалы жобалау тәсілдері мен жаңа заманғы жетілдірім жолдарын толық игеру керек болады.

Микропроцессорлық жүйенің негізін қалаушы және оның жұмысын жүзеге асырушы басты бөлігі - микропроцессор (МП) . Микропроцессор жүйеде информацияның өңделуін және оның жан-жақты жіберілімін бағдарлама арқылы басқарады. Қойылған мәселенің орындалу тәртібі сәйкесті бағдарламаға, яғни алынған микропроцессорға тән (яғни, оның командалар жүйесіне кіретін) командалар тізбесінің орындалуы арқылы жүзеге асырылады.

Микропроцессорлық жүйенің құрамына микропроцессормен қатар жады құрылымдары және информацияны енгізу/шығару құрылғылары (сыртқы құрылғылар) кіреді. Микропроцессорлық жүйелердің бастапқы даму барысында олар, микропроцессорлық жинам түрінде біріктірілген, бірге қолдануға жарамды (яғни, архитектурасы мен электрлік параметрлері бойынша сәйкестірілген) микросхемалар негізінде құрылды.

Микропроцессорлық жүйелердің (МПЖ) құрылым негізіне үш принцип алынған:

− модулдік;

− магистралдік;

− микробағдарламалы басқару.

Модулдік принцип жүйенің, қызметі жағынан толықтай бітірілген, жеке блоктар негізінде құрылатындығын сипаттайды. Әрбір модулдің, оны іске қосатын, рұқсат кірісі болады; ондағы сигнал деңгейі модулдің үшінші (жоғары кедергілі) жағдайын, яғни оның жүйе желісіне қосылу/қосылмауын басқарады.

Магистралдік принцип МПЖ-нің қызмет блоктарының арасындағы байланыс сипатын анықтайды; жүйенің барлық блогы өзара жүйелік магистраль (жүйе желісі) арқылы жалғанады және сол арқылы информация алмасады.

Микробағдарламалы басқару принципі жүйе бағдарламасын құруға пайдаланылатын командалардың әрбіреуінің қарапайым операциялар - микрокомандалар (информация жіберілімі, арифметикалық операциялар, ығыстырымдар және т. б. ) арқылы жүзеге асырылу мүмкіндіктерін сипаттайды.

Қазіргі заманда микропроцессорлық жүйелер, негізінде (80% шамасында), олардың қажетті қызмет бөліктері технологиялық тәсілмен құрамына енгізілген, микроконтроллерлерді пайдалану арқылы құрылады. Микропроцесорлар мен микропроцессорлық жинам микросхемаларының негізіндегі дәстүрлі микропроцессорлық жүйелер (олардың құрылу және реттелу процесінің күрделілігіне байланысты) қазіргі заманда сирек шығарылады. Микропроцессорлық жүйелердің бұл түрі, негізінде, өндірісте шығарылатын қалыпты микроконтроллерлердің қойылған талапқа сай сипаттамаларды қамтамасыз ете алмайтын жағдайында ғана құрылады.

Бұл тарауда микропроцессорлық жүйелердің құрылым принциптері мен жұмыс режимдері, құрама буындары мен олардың өзара байланыстарының жүзеге асырылым жолдары және олардың қазіргі заманғы құрылым және шығарылым түрлері жөнінде жалпы түсініктер беріледі.

1. 1. 1 Микропроцессорлық жүйенің орталық процессоры

Кез келген микропроцессорлық жүйенің орталық буыны - микропроцессор (Microprocessor), яғни жүйедегі информация өңделуі мен оның жан-жақты жіберілуі түгелдей осы микропроцессордың басқаруымен жүзеге асырылады. Микропроцессорлық жүйенің өзге буындары қосалқы қызметтер атқарады, олар: информацияны сақтау (оның ішінде басқару информациясын да, яғни жұмыс бағдарламасын да), сыртқы құрылғылармен байланыс, пайдаланушымен байланыс және т. б. Сонымен, процессор арифметикалық (қосу, алу және т. б. ), және логикалық (ығыстыру, салыстыру, кодтарды жасыру және т. б. ) функциялардың орындалуын, кодтардың уақытша сақталуын (оның ішкі регистрлерінде), кодтардың микропроцессорлық жүйенің құрама буындары арасында жіберілуін және т. б. жұмыстарды жүзеге асырады. Процессор орындайтын, бұндай қарапайым операциялардың саны жүздеген болуы мүмкін.

Процессор операцияларды тізбелеп (яғни, бірінен соң бірін, кезектеп), орындайды. Әрине, кейбір операцияларды параллель орындайтын процессорлар да бар, қатар істеуші бірнеше процессордан құрылған көппроцессорлы жүйелер де кездеседі, бірақ олар ерекше жағдайлар. Бір жағынан қарастырғанда, операциялардың тізбелі орындалуы информация өңделуінің кез келген күрделі алгоритмін жалғыз процессор арқылы жүзеге асыруға мүмкіндік береді. Бірақ, екінші жағынан, операциялардың тізбелі орындалуы жүйенің жұмыс алгоритмінің орындалу ұзақтығын оның күрделілігіне тәуелді қылады, яғни күрделі алгоритмдер қарапайым алгоритмдерге қарағанда баяуырақ орындалады. Өңделуші информация ағымын микропроцессорлық жүйенің жалғыз буыны - микропроцессор арқылы өткізу керек болғандықтан, оның тезәрекеттілігі онша жоғары болмайды. Дәстүрлі цифрлық жүйеде информация ағымының параллель орындалуын ұйымдастыру қиын емес, бірақ ол үшін схеманы күрделендіруге тура келеді.

Микропроцессордың кезекті мезетте қандай операция орындайтындығы басқару информациясымен, яғни бағдарламаның кезекті командасымен анықталады. Командалар (нұсқамалар) жинамы түріндегі бағдарламадағы әрбір команданың нақтылы кодын ажырату арқылы процессор осы мезетте не істеу керектігін біледі.

Процессордың орындай алатын командалары оның командалар жүйесін құрады. Процессордың командалар жүйесінің құрылымы мен көлемі оның тезәрекеттілігін, икемділігін, пайдаланылу ыңғайлылығын анықтайды. Командалар жүйесі, микропроцессордың түріне байланысты, жеке мәселелерді ғана шешуге икемделген (арнайы процессорларда) немесе алуан түрлі мәселелерді шешуге (әмбебап процессорларда) бағытталған болуы мүмкін. Команда кодтарының разряд саны әртүрлі болуы мүмкін (бір байттан бірнеше байтқа дейін) . Командалардың орындалу ұзақтығы әртүрлі, сондықтан командалар жинамы түріндегі жеке бағдарламаның түгелдей орындалу ұзақтығы бағдарламадағы командалар санына ғана емес, онда қандай командалардың пайдаланылғандығына да тәуелді болады.

Командалардың орындалуын қамтамасыз ету үшін процессордың құрамына келесі буындар енгізілген, олар: жалпы қызмет регистрлерінің жинағы, арифметикалық-логикалық құрылғы (АЛҚ, ALU - Arithmetic Logic Unit), арнайы регистрлер, мультиплексорлар, буферлер және т. б. қызмет буындары. Микропроцессор буындарының жұмысы процессордың жалпы сыртқы тактілік сигналдары арқылы сәйкестіріледі.

Микропроцессорлық жүйені құрушының процессордың ішкі құрылымы жөнінде, оның нақтылы кіріс сигналдарына және басқару кодтарына жауап ретінде қандай операция орындайтыны және қандай шығыс сигналдарын шығаратындығы туралы толық түсінігі болу керек. Олармен қатар, ол міндетті түрде, процессордың командалар жүйесін, оның жұмыс режимдерін және процессордың сыртқы әлеммен байланыс тәртібін (яғни, дерек алмастыру хаттамасын) білу керек.

1. 1. 2 Микропроцессорлық жүйенің байланыс жүйесі

Дәстүрлі байланыс құрылымында жүйе құрамындағы әрбір құрылғы өзінің сигналдары мен кодтарын өзге құрылғыларға тәуелсіз, жеке байланыс жолдары арқылы жібереді. Бұл жағдайда жүйедегі байланыс жолының саны да, ондағы дерек алмастыру хаттамасы да (шешілетін мәселеге байланысты) әртүрлі болады.

Микропроцессорлық жүйелердің құрамындағы әртүрлі құрылғылардың арасындағы дерек алмастырылу хаттамаларының әмбебаптылығы мен қарапайымдылығын қамтамасыз ету үшін желілік байланыс жүйесі деп аталатын құрылым қолданылады.

Желілік байланысты жүйелерде құрылғылар арасындағы сигналдардың барлығы да бір жолдармен, бірақ әртүрлі уақыт мезеттерінде жіберіледі (ол кезектелімді жіберілім деп аталады) . Жіберілімнің екі бағытта да жүзеге асырылуы мүмкін (ол екібағытты жіберілім деп аталады) . Нәтижесінде байланыыс жолдарының саны қысқарады және дерек алмастырылу тәртіптері (хаттамалары) қарапайымдалады. Сигналдардың немесе кодтардың жіберілетін жолдарының тобы желі (Bus) деп аталады.

Желілік байланыс құрылымында желіге қосылған құрылғылардың барлығының да дерек жіберуі немесе оны қабылдауы нақтылы тәртіппен (желі арқылы дерек алмастырылу хаттамасы бойынша) жүзеге асырылады.

Желілік байланысты жүйелер, негізінде, үш жағдайлы (3S, 3-state) шығысты микросхемалар арқылы құрылады. Ол микросхемалардың сәйкесті шығыстарын біріктіріп, кезектелімді немесе қосбағытты жолдар алуға мүмкіндік береді.

3S шығысты микросхемалардың қолданылымы кезінде жолға қосылған бір микросхеманың ғана шығыстары жандандырылып, ал өзгелерінің шығыстары үшінші (жоғарыкедергілі) жағдайында болуы қамтамасыз етілу керек.

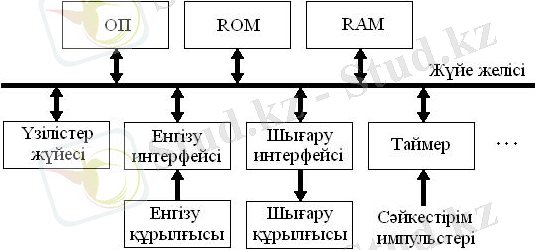

Қалыпты микропроцессорлық жүйенің құрамына кіретін негізгі құрылғылар (1. 1-сурет) :

− жүйеде информацияның өңделуін және оның жан-жақты жіберілімін жүзеге асыратын орталық процессор (ОП) ;

− жүйенің жұмыс бағдарламаларын сақтауға арналған тұрақты жады (ROM - Read Only Memory) ;

− жүйе жұмысына қажетті деректерді сақтауға арналған қызмет жадысы (RAM - Random Access Memory) ;

− микропроцессорлық жүйенің сыртқы құрылғылармен байланысын қамтамасыз етуші енгізу/шығару құрылғылары мен олардың сәйкесті интерфейстері.

1. 1 Сурет

Микропроцессорлық жүйенің құрамындағы құрылғылардың барлығы ортақ жүйе желісі арқылы біріктілген (ол жүйе магистралі немесе байланыс арнасы деп те аталады) . Жүйе магистраліне негізгі үш информациалық желі кіреді, олар:

− адрес желісі АВ (Address Bus) ;

− дерек желісі DB (Data Bus) ;

− басқарым желісі СВ (Control Bus) .

Дерек желісі - жүйе модулдерінің арасында дерек алмастырылуын қамтамасыз етуші, негізгі желі. Дерек желісі, оның деректерді екі бағытта да жіберуін қамтамасыз етуі керек болғандықтан, ол әрқашан екібағытты болады.

Адрес желісі - жадыға (немесе сыртқы құрылғыларға) нақтылы бағытталған байланысымды қамтамасыз етуші желі.

Магистралдың байланыс жолдарының толық санын кеміту үшін көбіне адрес желісі мен дерек желісін кезектестіру тәсілі қолданылады, яғни байланыс жолдары арқылы әртүрлі уақыт мезетінде адрес пен дерек кезектеп жіберіледі (цикл басында - адрес, цикл аяғында - дерек) .

Басқару желісінің жолдарындағы сигналдар кезекті цикл түрін анықтайды және оның әртүрлі кезеңдеріне сәйкесті уақыт мезеттерін бекітеді. Онымен қатар, басқару сигналдары процессордың (немесе магистралдың өзге қожасының, бастаушының, master) жұмысын жадының немесе енгізу/шығару құрылғыларының (орындаушы құрылғының, slave) жұмысымен келістіреді.

Негізгі басқару сигналдары - алмастыру стробтары, яғни жазу (шығару) стробы мен оқу (енгізу) стробы. Бұл сигналдарды процессор қалыптастырады, олар деректердің желі арқылы сәйкесті бағытта жіберілу мезеттерін анықтайды.

Микропроцессорлық жүйенің құрамындағы құрылғылардың барлығы да жүйе магистралына қосылған және олардың өзара информация алмасуы да осы магистраль арқылы жүзеге асырылады.

Енгізу/шығару құрылғыларын немесе сыртқы құрылғыларды (ЕШҚ немесе СҚ) жүйе магистралына қосу үшін олардың сигналдары нақтылы стандарттарға сәйкес келу керек, ол сәйкесті енгізу/шығару интерфейстері арқылы жүзеге асырылады.

1. 1. 3 Микропроцессорлық жүйенің жұмыс режимдері

Микропроцессорлық жүйені, жоғарыда айтылғандай, кез келген жұмысқа икемдеуге болады. Бұндай икемділік жүйенің орталық буыны -микропроцессор жұмысының сәйкесті бағдарлама (software) арқылы орындалуымен анықталады. Микропроцессорлық жүйенің аппараттық құрылымы (hardware) шешілетін мәселеге байланысты өзгертілмейді. Қойылған мақсатқа сәйкесті бағдарлама құрып, оны жүйе жадысына енгізу арқылы, микропроцессорды, жүйенің аппаратық мүмкіндігі жететін, кез келген мәселені шешуге бағыттауға болады. Бұның үстіне, микропроцессорлық жүйенің байланыстарының желілік ұйымдастырылуы оның аппараттық модулдерін жаңартуға, мысалы, жүйе жадысын бұрынғысынан көлемдірек немесе тезәрекеттілеу түрлеріне ауыстыруға, оған жаңа енгізу/шығару құрылғыларын қосуға, тіпті микропроцессордың өзін де одан қуаттырақ түріне ауыстыруға мүмкіндік береді.

Микропроцессорлық жүйенің шешілетін мәселеге икемделуіне оның жұмыс режимін (яғни, жүйелік магистраль арқылы дерек алмастырылу режимін) таңдау мүмкіндігі де көмектеседі.

Кез келген микропроцессорлық жүйеде оның магистралі арқылы информация алмастырылуы негізгі үш түрлі режимде жүзеге асырылады, олар:

− бағдарламалы-басқарылымды алмастыру;

− үзілістер арқылы алмастыру (Interrupts) ;

− жадыға тура шығу арқылы алмастыру (ЖТШ, DMA - Direct Memory Access) .

Олардың ішіндегі негізгісі - біріншісі, онсыз қалған алмастыру режимдері орындалмайды. Бұл режимде процессор жүйелік магистралдың жеке қожасы (Master) болады, яғни жүйе құрамындағы құрылғылар арасында информация алмастырылуы, орындалушы бағдарламаның анықтаған тәртібі бойынша, процессордың басқаруымен ғана жүзеге асырылады. Процессор жадыдан команда кодтарын оқиды (таңдап шығарады), сосын оларды орындап (яғни, жадыдан немесе енгізу/шығару құрылғысынан алынған деректерді осы командаларға сәйкесті өңдеп), өңдеу нәтижелерін жадыға жазады немесе енгізу/шығару құрылғысына жібереді.

Үзілістер арқылы дерек алмастыру микропроцессорлық жүйенің сыртқы оқиғаға немесе сырттан түскен сигналға байланысты кезексіз әрекетінің қажетті жағдайында пайдаланылады. Сыртқы оқиғаға байланысты әрекетті келесі жолдармен ұйымдастыруға болады:

− сыртқы оқиғаның туғанын бағдарламалық тәсілмен бақылап отыру арқылы (ту тексеру тәсілі немесе Polling) ;

− оқиғаның туғаны туралы сыртқы құрылғының жіберген үзіліс сұранысы арқылы (IRQ - Interrupt ReQuest) .

Екі жағдайда да процессор негізгі бағдарламаға байланысты кезекті жұмысын уақытша тоқтатып, сыртқы оқиғаға байланысты іс-әрекетке ауысады да, бұл жұмыс біткеннен кейін негізгі бағдарламаның жұмысына қайтып келеді. Үзілістер арқылы дерек алмастыру кезінде, бағдарламалы алмастырудағы сияқты, магистралдағы барлық сигналды процессор қояды, яғни үзіліске байланысты жұмыс та толықтай процессордың басқаруымен жүзеге асырылады.

Жадыға тура шығу режимінде (DMA - Direct Memory Access) қызмет қажет қылған сыртқы құрылғы процессорға сәйкесті сұраныс жібереді, оған жауап ретінде микропроцессор кезекті команданың орындалуын бітіргеннен кейін жүйе желісінен ажырап, сұраныс жіберген құрылғының жұмысына рұқсат береді. Жадыға тура шығу арқылы, негізінде, енгізу/шығару құрылғысы мен жады арасындағы информация жіберілуі жүзеге асырылады. Жадыға тура шығу арқылы дерек жіберілімін процессор емес, арнайы контроллер (ЖТШ контроллері) басқарады. Магистралді сұрап алған құрылғының жұмысы біткеннен кейін, магистраль босатылып, процессордың қарауына беріледі де, ол уақытша тоқтатылған негізгі бағдарламаның жұмысын жалғастырады.

1. 1. 4 Микропроцессорлық жүйенің архитектуралары

Осы кезеңге дейін біз микропроцессорлық жүйенің бір түрін, атап айтқанда ортақ желілі архитектурамен (ол Принстон немесе фон-Нейман архитектурасы деп аталады) құрылған түрін қарастырдық. Бұндай құрылымда деректер мен командалар бір жадыда сақталады және олар жалғыз ортақ желі арқылы жіберіледі (1. 2-сурет) .

1. 2 Сурет

Микропроцессорлық жүйе архитектурасының бұдан басқа түрі де бар, ол - жеке желілі архитектура (ол Гарвард архитектурасы деп аталады) . Бұндай құрылымда деректер мен командалар олардың өздеріне арналған дербес жадыларда сақталады және олар әрбіреуіне сәйкесті дербес желілері арқылы жіберіледі (1. 3-сурет) .

1. 3 Сурет

Ортақ желілі (фон-Нейман) архитектура екі желіге қатар жұмыс істеуді және олар арқылы дерек жіберілуін қатар бақылауды қажет қылмайды. Деректер мен командалардың жалғыз жадыда сақталуы жадыны олардың көлеміне байланысты бөлуге мүмкіндік береді. Мысалы, кейбір жағдайда күрделі және үлкен көлемді бағдарлама керек болып, ал деректер онша көп болмауы мүмкін. Басқа жағдайда, керісінше, бағдарлама қарапайым, ал деректер үлкен көлемді болуы мүмкін. Жады аймағын осы жағдайларға байланысты бөлу ешқандай қиындық тудырмайды, әйтеуір - деректер мен командалар жүйе жадысына сыйса болды. Әдетте, осындай архитектуралы жүйелердің жадысы үлкен мөлшерлі болады (ондаған және жүздеген мегабайт) . Ортақ желілі архитектура көбірек таралған, мысалы, дербес компьютерлерде осы архитектура қолданылады.

... жалғасы- Іс жүргізу

- Автоматтандыру, Техника

- Алғашқы әскери дайындық

- Астрономия

- Ауыл шаруашылығы

- Банк ісі

- Бизнесті бағалау

- Биология

- Бухгалтерлік іс

- Валеология

- Ветеринария

- География

- Геология, Геофизика, Геодезия

- Дін

- Ет, сүт, шарап өнімдері

- Жалпы тарих

- Жер кадастрі, Жылжымайтын мүлік

- Журналистика

- Информатика

- Кеден ісі

- Маркетинг

- Математика, Геометрия

- Медицина

- Мемлекеттік басқару

- Менеджмент

- Мұнай, Газ

- Мұрағат ісі

- Мәдениеттану

- ОБЖ (Основы безопасности жизнедеятельности)

- Педагогика

- Полиграфия

- Психология

- Салық

- Саясаттану

- Сақтандыру

- Сертификаттау, стандарттау

- Социология, Демография

- Спорт

- Статистика

- Тілтану, Филология

- Тарихи тұлғалар

- Тау-кен ісі

- Транспорт

- Туризм

- Физика

- Философия

- Халықаралық қатынастар

- Химия

- Экология, Қоршаған ортаны қорғау

- Экономика

- Экономикалық география

- Электротехника

- Қазақстан тарихы

- Қаржы

- Құрылыс

- Құқық, Криминалистика

- Әдебиет

- Өнер, музыка

- Өнеркәсіп, Өндіріс

Қазақ тілінде жазылған рефераттар, курстық жұмыстар, дипломдық жұмыстар бойынша біздің қор #1 болып табылады.

Ақпарат

Қосымша

Email: info@stud.kz