CISC архитектуралы біркристалды микроконтроллердер: архитектурасы, басқару блогы және кіріс-шығыс порттары

Жұмыс түрі: Курстық жұмыс

Тегін: Антиплагиат

Көлемі: 23 бет

Таңдаулыға:

ҚАЗАҚСТАН РЕСПУБЛИКАСЫ БІЛІМ ЖӘНЕ ҒЫЛЫМ

МИНИСТРЛІГІ

М. ӘУЕЗОВ атындағы ОҢТҮСТІК ҚАЗАҚСТАН МЕМЛЕКЕТТІК УНИВЕРСИТЕТІ

Автоматтандыру, ТЕЛЕКОММУНИКАЦИЯ және

БАСҚАРУ кафедрасы

КУРСТЫҚ ЖҰМЫС

пәні «Цифрлық құрылғылар және микропроцессорлар»

мамандығы: Радиотехника, электроника және телекоммуникациялар

тақырыбы: CISC архитектуралы микроконтроллерлер

Жұмыс

Бағасы

Бағасына қорғалды

«___» 2015_ж.

Комиссия

қолы, аты - жөні

қолы, аты - жөні

Норма бақылау:

қолы, аты - жөні

Орындаған

Студент

Тобы -

қолы, аты - жөні,

Жетекші

қолы, аты - жөні,

Шымкент 2015 ж.

Ф. 7. 05-04

М. О. Әуезов атындағы Оңтүстік Қазақстан мемлекеттік университеті

Автоматтандыру, ТЕЛЕКОММУНИКАЦИЯ және

БАСҚАРУ кафедрасы

«Бекітемін»

Кафедра меңгерушісі

Исмаилов С. Ө. т. ғ. к., доцент

2015ж.

«Цифрлық құрылғылар және микропроцессорлар»

пәні бойынша курстық жұмыс

ТАПСЫРМА № 13

Студент тобы

Жұмыс тақырыбы: CISC архитектуралы микроконтроллерлер

Бастапқы мәліметтер жоқ

Әдебиет:

1. Б. С. Есмағамбетов. «Цифрлық құрылғылар және микропроцессорлар» пәні бойынша әдістемелік нұсқау

2. Есмағамбетов Б. С. Цифрлық құрылғылары және микропроцессорлар. Оқу құралы. Шымкент: «Нұрлы бейне» баспасы, 2010, 184с

3. Есмағамбетов Б. С. Басқару жүйелердргі микропро-цессорлық кешендер. Оқу құралы. Шымкент: «Әлем баспасы», 2013, 236с

Тапсырманың берілген күні , жұмысты қорғалған күні

Жұмыстың жетекшісі:

(аты - жөні, қолы)

Тапсырманы орындауға қабылдаған

(күні, студенттің қолы)

Ф. 7. 04-06

Қазақстан республикасы білім және ғылым министрлігі

М. О. Әуезов атындағы Оңтүстік Қазақстан мемлекеттік университеті

«Ақпараттық технологиялар және энергетика» жоғары мектебі

«Автоматтандыру, телекоммуникация және басқару» кафедрасы

«Бекітемін»

Кафедра меңгерушісі

Исмаилов С. Ө. т. ғ. к., доцент

«»2015ж.

Курстық жұмыс қорғау

Хаттамасы № 13

пәні: «Цифрлық құрылғылар және микропроцессорлар»

студент тобы -

(аты - жөні)

Курстық жұмыс тақырыбы CISC архитектуралы микроконтроллерлер

Қорғау кезінде келесі сұрақтарға жауап алынды:

Курстық жұмысты орындау кезінде алынған балл (60 мүмкіндіктен) , қорғау бағаланды (40 мүмкіндіктен ) балл.

Сомалық баллы

Жұмыстың бағасы

Курстық жұмыстың жетекшісі

Комиссия мүшелері

Комиссия мүшелері

Қорғау күні 2015ж.

Аннотация

Соңғы кезде өндірістік технологиялық процестерінде қолданылатын машиналар мен жабдықтардың көбісінде басқару әрекеттері цифрлық аппаратурамен жүзеге асады. Басқаруды бір мақсатқа бағытталған ақпараттың өзгеруі деп қарастырғанда, мұндай аппаратура микропроцессордың ақпарат өңдейтін мүмкіндігін пайдаланады. Осы тұрғыдан қарағанда, курстық жұмысында қарастырылған мәселелер CISC архитектуралы микроконтроллерлермен танысуға жол ашады.

Курстық жұмысында CISC біркристалды микроконтроллерлер архитектурасы, басқару блогы, кіріс-шығыс порттары қарастырылған.

Көлемі 30 бет, 14 сурет, 2 кесте, 7 әдебиет қолданылған.

Мазмұны

Нормативтік сілтемелер 6

Пайданылатын қысқартулар мен белгілер 7

Кіріспе 8

- CISC біркристалды микроконтроллерлердің

архитектурасы 9

2. Басқару блогы 153. Кіріс-шығыс порттары 18

Нормативті сілтемелерПайдаланылған әдебиеттері 27

Қолданылған қысқартулар мен белгілер

МП - микропроцессор

ЭЕМ - электронды есептеу машина

ТЕСҚ - тұрақты есте сақтағыш құрылғы

ОЕСҚ - оперативті есте сақтағыш құрылғы

АЦТ - аналогты -цифрлық түрлендіргіш

БМК - біркристалды микроконтроллер

ҮИС - үлкен интегралды микросхема

ОП - орталық процессор

ББ - басқару блогы

ЖМР - жалпы міндет регистірі

АЛҚ - арифметикалық-логикалық құрылғы

БРЖ - бағдарламаның резидентті жады

ДРЖ - деректердердің резидентті жады

Кіріспе

Тақырыбының өзектілігі .

Курстық жұмыстың өзектілігі тақырыб бойынша қарастылылған мателиалдардың микропроцессорлық техникада пайдалуымен анықталады.

Курстық жұмыстың мақсаттары мен міндеттері микропроцессорлық техникадағы пайдаланатын құрылғыларды қолдану принциптеріне негізделеді.

Практикалық қажеттілігі.

Курстық жұмыстың практикалық қажеттілігі қарастырылған принциетері, құрылымдық схемалары, сипаттамалары әр-түрлі цифрлық техникада қолдану мұмкіндіктерімен анықталады.

Курстық жұмыстың мазмұны тапсырманың және әдістемелік нұсқаудың талаптарына сәйкеседі [1] .

1 CISC біркристалды микроконтроллерлердің архитектурасы

ҮИС (БИС) - ің бір корпусында конструктивті орындалған, микропроцессорлық жүйенің барлық компонентін, яғни жүйелі блок, берілгендер жады, бағдарламалар жады, бағдарламаланатын интерфейстерді, өзінде ұстайтын құрылғылар біркристалды микроконтроллер (БМК) болып табылады [10] . Біркристалды микроконтроллерлердің ерекшеліктері:

- командалар жүйесі басқару және реттеу есептерді орындауға бағытталған;

- БМК-да жүзеге асырылатын алгоритмдер, сыртқы сигналдардың тәуелділігінен бірнеше түрге бөлінуі мүмкін;

- БМК пайдаланатын берілгендер үлкен разрядтылыққа ие болмауы керек;

- БМК-і пайдаланатын басқару жүйелерінің схемалы түрде жүзеге асырулуы қиын емес және үлкен бағаға ие емес;

- біркристалды МП жүйелеріне қарағанда әмбебаптылық және басқару функциясын кеңейту мүмкіндігі әлдеқайда төмен.

Біркристалды микроконтроллерлер бүгінгі құрылған әртүрлі құралдарды, мысалы, автомобильді электрониканы, тұрмыстық техниканы, ұялы телефондарды құруға және оларды басқаруға арналған ыңғайлы құрал-жабдық болып табылады.

Біркристалды микроконтроллерлердің архитектурасы және функционалдық мүмкіндіктері

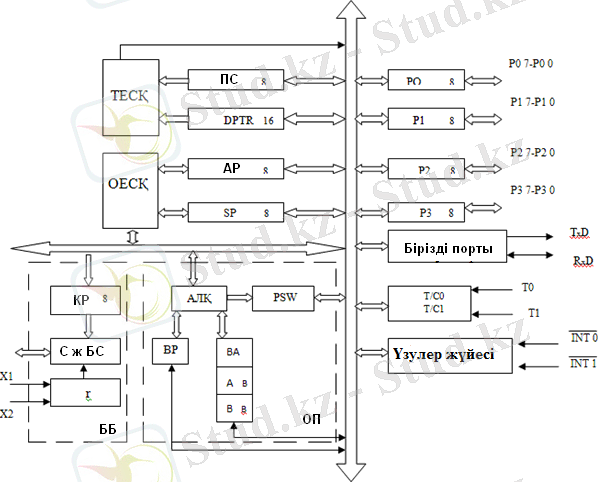

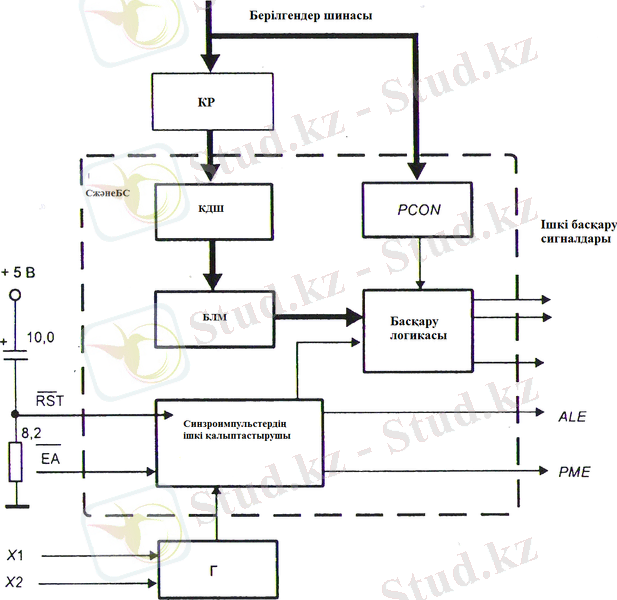

БМК-ың құрылымын және негізгі блоктардың жұмыс істеуды К1816ВЕ51 (i80x51) ҮИС мысалында қарастырамыз (сурет 1) .

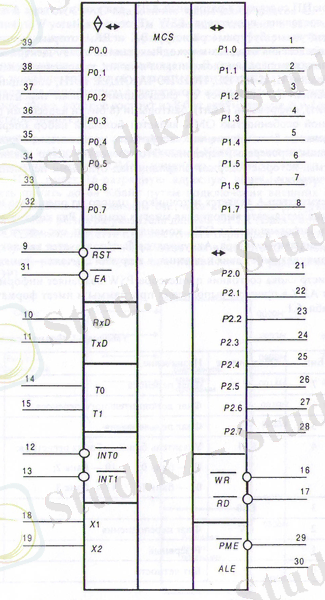

Микросхеманың графикалық бейнеленуі 2 суретте көрсетілген.

БМК құрылымдық схемасы қамтиды:

- орталық процессорының (ОП) 8 разрядты блогы;

- сыйымдылығы 4Кбайт ТЕСҚ (тұрақты есте сақтау құрылғы) бағдарлама жады;

- сыйымдылығы 128 байт ОЕСҚ (оперативті есте сақтау құрылғы) берілгендер жады;

- төрт 8 разрядты бағдарламаланатын кіріс/шығыс P0-P3 порты;

- тізбектік;

- екі 16-разрядты бағдарламаланатын таймер/есептегіш Т/C0, Т/C1;

- бес векторлы және екі деңгей басымдылығы бар үзу жүйесі;

- басқару блогы (ББ) .

Сурет 1. БМК К1816ВЕ51 құрылымдық схемасы

Орталық процессор (ОП) блогы 8 разрядты АЛҚ-ан (арифметикалық-логикалық құрылғы), екі (А және В) аккумулятордан, PSW (Processor State Word) процессорының сөздің күй регистрден және бағдарламалық-жетпес ВА және ВР буферлік регистрлерден (олар кіріс және бастапқы берілгендерін тарататын функцияны атқарады) құрайды. Орталық процессор қосу, алу, көбейту, бөлу, И (және), ИЛИ (немесе), НЕ (емес), жылжыту, түсіру (нольды орнату) операцияларын орындайды. Ол келесі айнымалылармен жұмыс жасайды: логикалық (1 бит), сандық (4 бит), байттық (8 бит), және адрестік

Сурет 2. БМК К1816ВЕ51 графикалық белгіленуі

(16 бит) . БМК мінездемелік ерекшелігі - биттармен көптеген операцияларды орындауы: айнымалылардың бөлек биттерін орнатылуы, түсіруы, терістеуы, тексерілуы, тапсырылуы болуы мүмкін. Бұл «иә-жоқ» («true-false») операцияға ұқсас операциялармен алгоритмдерді оңай жүзеге асыруға мүмкіндік береді.

Кесте 1. PSW сөз күй форматы

Жұмысшы регистрлердің банктерінің көрсеткіші:

00- банк 0; 10- банк 2;

01- банк 1; 11- банк 3

Ескерту. А - бит аппаратты түрде орнатылады, Б - бағдарлама түрінде.

А аккумуляторы бір оператордың көзі және көптеген командалардың орындалу нәтижесінің орыны болып табылады. Бірнеше командалар қатары, мысалы, ОЕСҚ-дан ақпаратты алу және беру, Test, Inc, Dec командалары ак-

кумулятордың қатысуынсыз орындалуы мүмкін. В аккумуляторы көбейту және бөлу командаларында ғана аккумулятор ретінде, ал қалған жағдайда-жалпы міндет регистірдің (ЖМР) бірі ретінде қолданылады.

PSW процессорының сөз күй регистрі бағдарламаны орындау барысындағы және форматқа ие АЛҚ-ның 1 кестеде келтірілген күйін сақтайды. С, АС жалауларының міндеті i8086 МП CF, AF жалауларының міндетіне сәйкес. OV жалауы қосу және алу командаларында орнатылады, егер нәтиже 7-разрядты тордың сыйымдылығынан асатын болса және үлкен бит белгі ретінде анықталмаған болса; бөлу командасында OV тасталады, ал нөлге бөлгенде - орнатылады. Көбейту командаларында, егер нәтиже OFFH артық болса, онда OV логикалық бірлікке ие болады. Р жалауы А аккумулятордың ішіндегісін тақтылыққа толықтырып тұрады, яғни 9 разрядты сөз (аккомулятордың 8 биті және Р биті) әрқашан бірліктің тақ санына ие.

Тұрақты есте сақтау құрылғысы немесе бағдарламаның резидентті жады (БРЖ) ақпараттық сыйымдылығы 4 Кбайт маскалық типі бойынша жасалған ТЕСҚ. Басқа БМК, мысалы, K181G751, EPROM типтегі ТЕСҚ ие. ТЕСҚ-да 16-разрядты адрестік шинасы бар, ол жадты 64 Кбайт-қа дейін сыртқы ҮИС-ті қосу арқылы ұлғайтуға мүмкіндік береді. Адрес ПC программалық санаушының (PC-Program Counter) мазмұнымен немесе берілгендердің DPTR (Data Pointer Registers) көрсеткіш регистрінің мазмұнымен анықталады. DPTR регистрі жанама өтулерде немесе кестелердің адрестелуінде қолданылады. Сонымен қатар, ЖМР ретінде, немесе 16 разрядты регистрдің бірі ретінде, немесе екі тәуелсіз 8 разрядты DPH және DPL регистрлер ретінде қолданылуы мүмкін.

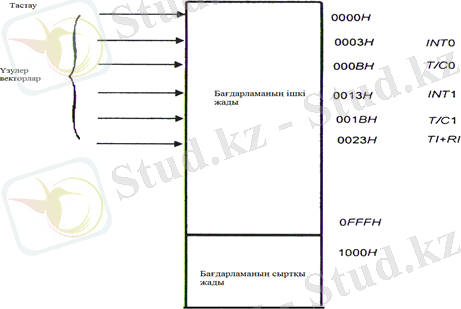

Сурет 3. БРЖ адрестік кеңістігінің таралуы

ТЕСҚ -да адрестік кеңістіктің таралуы 3. суретте көрсетілген. ТЕСҚ -дағы нөлдік адрес БМК - дегі тастаудан кейінгі бағдарламаның орындалу басын анықтайды. (003H, 00BH, 013H, 01BH, 023H) кіші адрестер үзулерді өңдейтін қосымша бағдарламалардың бастапқы адресі болып табылады.

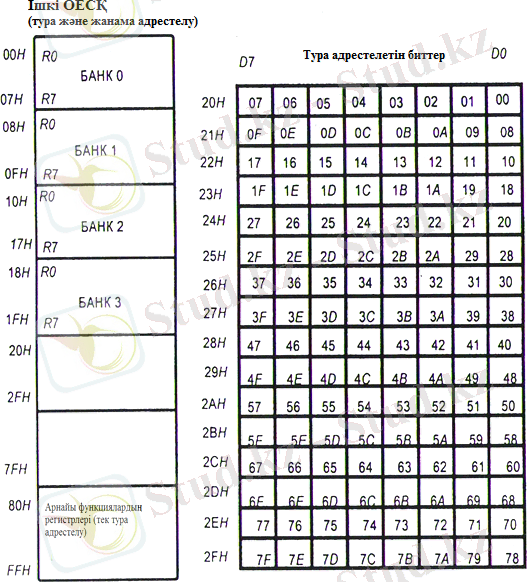

Оперативті есте сақтау құрылғысы (ОЕСҚ) немесе деректердердің резидентті жады (ДРЖ) екі аймақтан тұрады (сурет 6. 4) . Бірінші аймақ - 0-7FH адресінде орналасқан ақпараттық сыйымдылығы 128 x 8 бит болатын берілгендердің ОЕСҚ. Екінші аймақ - 80H-FFH адресінде орналасқан арнайы функциялар регистрлер (SFR, Special Function Registers) .

Сурет 4. Берілгендердің резидентті жады

Берілгендердің резидентті жады 8-разрядты регистрлердің адресімен (РА) немесе стек көрсеткішімен (SP) адрестеледі (1 суретті қара) . Адрес регистрі ОЕСҚ - да команданы орындау барысында ұяшықтың адресі жүктелетін бағдарламалық - қолжетімсіздік регистрі болып табылады. SP регистрі ДРЖ бөлігі болып табылатын стекті адрестеуге арналған. SP мазмұны берілгендерді стекте сақтау алдында PUSH және CALL командалары бойынша 1-ге көбейеді және POP және RET командалары бойынша 1-ге азайяды. Стек элементтерінің мұндай адрестелуін инкрементке дейін/декременттен кейін деп атайды. БМК инициализация процесінде SP-ға RESET сигналы түскеннен кейін автоматты түрде 07Н коды жүктеледі. Бұл, егер бағдарлама стекті жаңадан анықтай алмаса, онда стектегі берілгендердің бірінші байты ДРЖ ұяшығында 08Н адресімен орналасады деген сөз.

Берілгендердің резидентті жады сыртқы ҮИС-ң қосылуымен 64 Кбайтқа дейін ұлғаю мүмкін.

2. Басқару блогы

Басқару блогы тактілі сигналдардың генераторынан (Г), бағдарламалық - қолжетімсіздік команда регистрі (КР), синхронизация және басқару схемасынан (С және БС) тұрады (1 суретті қара) . Басқару блогының құрылымдық схемасы 5 суретте көрсетілген.

Сурет 5. Басқару блогының құрылымдық схемасы

БРЖ - дан саналған команда коды 8 разрядты КР жазылады және С және БС-ның құрамына кіретін команда дешифраторына (КДШ) келіп түседі. Команда дешифраторы бағдарламаланатын логикалық матрицаға (БЛМ), одан кейін логикалық басқару блогына келіп түсетін 24 разрядты кодты қалыптастырады.

Логикалық басқару блогы декодталған команда коды, (жалпы тастау сигналы), (БРЖ жұмысын блоктау сигналы) сыртқы басқару сигналдары және ішкі синхроимпульстерді қалыптастырушының сигналдары негізінде ішкі басқару сигналдарын тудырады.

Ішкі синхроимпульстерді қалыптастырушы қалыптастырады:

- машиналық циклды синхрондау ішкі сигналдарды;

- ALE адресінің белгілеуге рұқсат ететін бастапқы сигналды;

- бағдарлама жадыға рұқсат ететін PME сигналды (тек сыртқы жадымен жұмыс істегенде қалыптасады) .

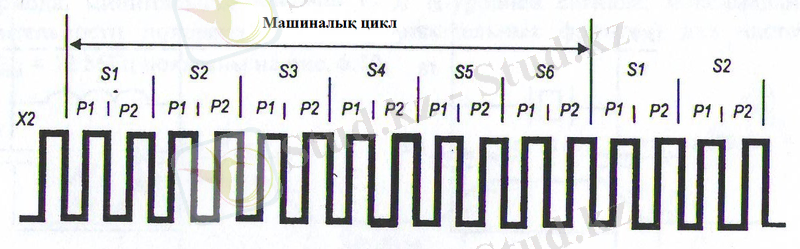

Машиналық цикл (6-сурет) бекітілген ұзақтыққа ие және әрқайсысы ұзақтығы бойынша бір тактке тең S1- S6 алты күйді қамтиды.

Сурет 6. БМК машиналық циклдарды қалыптастыру диаграммасы

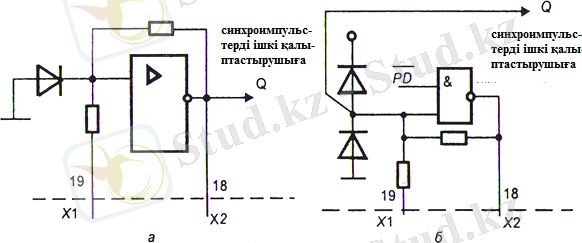

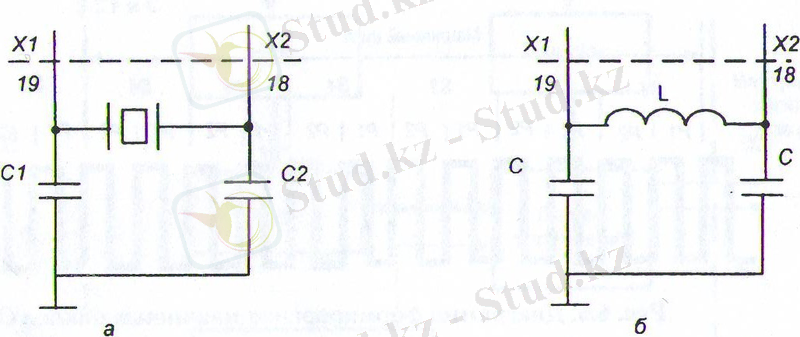

Әр күй немесе такт P1 және P2 екі фазадан тұрады. Фазаның ұзақтығы Q сигналының периодына тең. Ол, БМК кварцті резонаторының 18 (XTL2) және 19(XTL1) (8, а сур. ) шығыстарына немесе LC-тізбекті (8, б сурет) қосылуынан, ішкі тактілік генератордан (7 сур) немесе сыртқы тактілік сигналдардың көзінен (9 сур. ) қалыптасады.

8, a суреттегі схемада көрсетілген генераторының импульстердің жиілігі төмендегідей анықталады:

мұндағы

Cpp 10пф - ҮИС шығыстарының сыйымдылығы.

Сурет 7. Ішкі тактілік генераторлардың принциптік схемасы:

a-n-МДП-технологиясы; б-К- МДП-технологиясы;

Сурет 8. Ішкі тактілік генераторлардың сыртқы тізбектері:

a- кварцті резонаторды қосу; б- LC-тізбегін қосу

Тактілік сигналдардың сыртқы көздерінің БМК қосылуы n-МДП (9, a суретті қара) және К- МДП (9, б суретті қара) технологиясы бойынша жасалған. Бірінші жағдайда синхрондау сыртқы импульстер 18 (XTL2) және 19(XTL1) шығыстарына келіп түсуімен ерекшеленеді. Ал екінші жағдайда синхрондау сыртқы импульстер 19(XTL1) және 20 (жалпы) шығысына келіп түседі, ал 18 (XTL2) шығысы қосылмаған күйде қалады.

Кварцті резонатордың жиілігі немесе синхрондау сыртқы импульстердің тактілік жиілігі 12МГц - ке тең болған кезде машиналық циклдің ұзақтығы 1мкс - ке тең болады.

Сурет 9. Тактілік сигналдардың сыртқы көзінің қосылуы

a- n-МДП үшін; б- К- МДП үшін

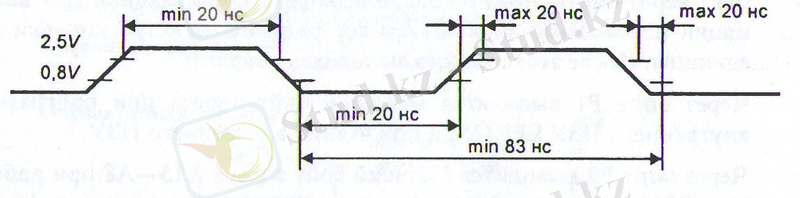

=12 МГц жиілікке арналған синхрондау сыртқы импульстердің параметрлері (периодтың минималды мәні, сигналдың L және Н-деңгейлердің минималды уақыты, оң және теріс фронттардың максималды ұзақтығы) 10 суретте көрсетілген.

Сурет 10. Синхрондау сыртқы импульстердің параметрлері

Басқару блогына энергияны пайдалануды басқару РСОN (Power CONtrol) регистрі кіреді (5. 5 суретті қара) .

3. Кіріс-шығыс порттары

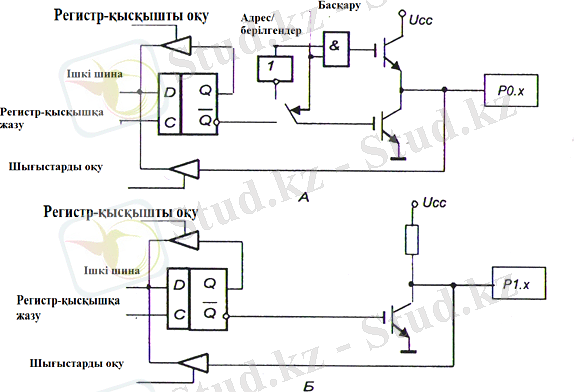

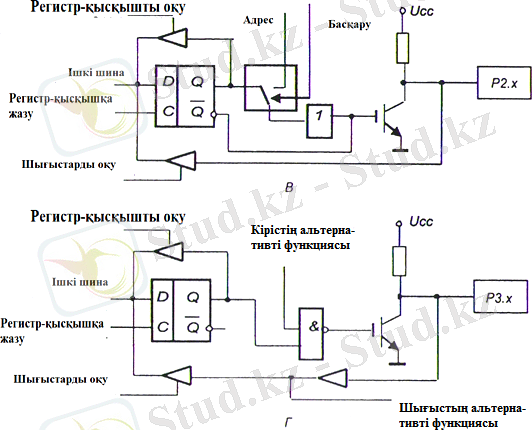

P0-P3 кіріс/шығыс порттары (1 суретті қара) БМК ішкі құрылғылармен 32 кіріс/шығыс арнасымен байттық ақпарат алмасу үшін арналған. P0-P3 порт арналарының принциптік схемасы 11 суретте көрсетілген. Әр порт арнасы басқарылатын регистр-қысқыштан, екі буферден және шығыс транзистор каскадтан тұрады. Порттарының кіріс және шығыс сигналдарының деңгейлері ТТЛ-логика стандартына сәйкес келеді. Кез келген порт арнасын басқа арналардан тәуелсіз ақпаратты енгізуге және шығаруға қолдануға болады. Порт арнасын кіріс үшін қолдану керек болса, регистр-қысқышының сәйкес келетін D-триггерге логикалық бірлікті жазу керек. Оның кернеуі шығыс каскадтың МДП- транзисторды жабады.

Порттардың физикалық адресі төмендегідей:

- P0-80H, биттік адрестеудеа 80H-87H;

- P1-90H, биттік адрестеуде 90H-97H;

- P2-A0H, биттік адрестеуде A0H-A7H;

- P3-B0H, биттік адрестеуде B0H-B7H;

Порт P0 екібағытты болып табылады, себебі ол арқылы кез келген уақытта ақпаратты енгізуге және шығаруға болады. P0 портының шығысының үш күйі бар. P0 порты арқылы:

- сыртқы ТЕСҚ мен және сыртқы ОЕСҚ мен жұмыс жасау кезінде A7-A0 адресінің кіші байты шығарылады;

- сыртқы жадпен жұмыс жасағанда берілгендердің байты БМК-дан алынады және БМК-ға беріледі. Берілгендердің байттын айырбастауы және сыртқы жадтың адрестің кіші байтыны шығаруы уақыт бойынша бір мезгілде өтеді;

- ішкі ТЕСҚ (EPROM) бағдарламалау барысында берілгендер беріледі.

P1-P3 порттары квазиекібағытты болып табылады, себебі кез келген уақытта порттар арқылы тек қана ақпаратты шығаруға болады. Ақпаратты енгізу үшін регистр-қысқыштың барлық разрядына логикалық бірлікті жазу керек. Осыдан кейін кірісті орындауға болады.

P1 порты арқылы ішкі ТЕСҚ (EPROM-ды) бағдарламалауда және ішкі ТЕСҚ-ны оқуда адрестің кіші байт шығарылады.

P2 порты арқылы сыртқы ТЕСҚ және сыртқы ОЕСҚ-мен жұмыс жасағанда адресінің A15-A8 үлкен байты шығарылады (егер, адрес 16-разрядты болса) ; ішкі ТЕСҚ (EPROM) бағдарламалауда және оқу барысында адресінің A15-A8 үлкен байты беріліді.

P3 порты ақпаратты енгізу/шығару үшін, сондай-ақ ақпаратты алмасудың альтернативті функциясын жүзеге асыруда қолданылады (11, г суретті қара) . Альтернативті функциялар 2 кестеде келтірілген. P3 портының әр сегіз арнасын пайдаланушы альтернативті функциялардың орындалуына бағдарламалай алады. Ол үшін P3 порттың регистр-кілтінің (P3. 0-P3. 7) сәйкес келетін разрядтарына бірлікті жазады.

Тізбектік порты (1 суретті қара) берілгендермен кезекті алмасуды қамтамасыз ету үшін арналған. Бұл порт жылжыту регистрі немесе әмбебап асинхрондық қабылдағыш-тапсырғыш ретінде қолданылуы мүмкін. Соңғы жағдайда айырбастау жылдамдығы белгіленген немесе айнымалы болу мүмкін және дуплекстік режимінде жұмыс істей алатын мүмкіндігі бар. Тізбектік порты төрт режимінің бірінде жұмыс істей алады (0 режим, 1 режим, 2 режим, 3 режим) . Оларды SCON (Serial port CONtrol) регистрге басқару сөзін жазу арқылы таңдауға болады.

Сурет 11. Порт арналарының принциптік схемасы:

a-P0; б-P1; в-P2; г-P3

Кесте 2. P3 портының альтернативті функциялары

0 режимінде тізбектік порты 8-разрядты жылжыту регистрін танытады. Ақпараттың байты RxD шығысы арқылы беріледі және алынады, сонымен қатар TxD шығысы арқылы жылжудың синхронизация сигналы беріледі. Байтты қабылдау және беру кіші разрядтан басталып және үлкен разрядпен аяқталады. Алмасу жылдамдығы бекітілген және f/12-ке тең, бұл жердегі f - БМК синхрондау жиілігі.

... жалғасы- Іс жүргізу

- Автоматтандыру, Техника

- Алғашқы әскери дайындық

- Астрономия

- Ауыл шаруашылығы

- Банк ісі

- Бизнесті бағалау

- Биология

- Бухгалтерлік іс

- Валеология

- Ветеринария

- География

- Геология, Геофизика, Геодезия

- Дін

- Ет, сүт, шарап өнімдері

- Жалпы тарих

- Жер кадастрі, Жылжымайтын мүлік

- Журналистика

- Информатика

- Кеден ісі

- Маркетинг

- Математика, Геометрия

- Медицина

- Мемлекеттік басқару

- Менеджмент

- Мұнай, Газ

- Мұрағат ісі

- Мәдениеттану

- ОБЖ (Основы безопасности жизнедеятельности)

- Педагогика

- Полиграфия

- Психология

- Салық

- Саясаттану

- Сақтандыру

- Сертификаттау, стандарттау

- Социология, Демография

- Спорт

- Статистика

- Тілтану, Филология

- Тарихи тұлғалар

- Тау-кен ісі

- Транспорт

- Туризм

- Физика

- Философия

- Халықаралық қатынастар

- Химия

- Экология, Қоршаған ортаны қорғау

- Экономика

- Экономикалық география

- Электротехника

- Қазақстан тарихы

- Қаржы

- Құрылыс

- Құқық, Криминалистика

- Әдебиет

- Өнер, музыка

- Өнеркәсіп, Өндіріс

Қазақ тілінде жазылған рефераттар, курстық жұмыстар, дипломдық жұмыстар бойынша біздің қор #1 болып табылады.

Ақпарат

Қосымша

Email: info@stud.kz