Микропроцессорлық техникада жүйені тестілеу мәселелері

Жұмыс түрі: Курстық жұмыс

Тегін: Антиплагиат

Көлемі: 29 бет

Таңдаулыға:

ҚАЗАҚСТАН РЕСПУБЛИКАСЫ БІЛІМ ЖӘНЕ ҒЫЛЫМ

МИНИСТРЛІГІ

М. ӘУЕЗОВ атындағы ОҢТҮСТІК ҚАЗАҚСТАН МЕМЛЕКЕТТІК УНИВЕРСИТЕТІ

Автоматтандыру, ТЕЛЕКОММУНИКАЦИЯ және

БАСҚАРУ кафедрасы

КУРСТЫҚ ЖҰМЫС

пәні «Цифрлық құрылғылар және микропроцессорлар»

мамандығы: Радиотехника, электроника және телекоммуникациялар

тақырыбы: Микропроцессорлық техникада жүйені тестілеу мәселелері

Жұмыс

Бағасы

Бағасына қорғалды

«___» 2015_ж.

Комиссия

қолы, аты - жөні

қолы, аты - жөні

Норма бақылау:

қолы, аты - жөні

Орындаған

Студент

Тобы -

қолы, аты - жөні,

Жетекші

қолы, аты - жөні,

Шымкент 2015 ж.

Ф. 7. 05-04

М. О. Әуезов атындағы Оңтүстік Қазақстан мемлекеттік университеті

Автоматтандыру, ТЕЛЕКОММУНИКАЦИЯ және

БАСҚАРУ кафедрасы

«Бекітемін»

Кафедра меңгерушісі

Исмаилов С. Ө. т. ғ. к., доцент

2015ж.

«Цифрлық құрылғылар және микропроцессорлар»

пәні бойынша курстық жұмыс

ТАПСЫРМА № 15

Студент тобы

Жұмыс тақырыбы: Микропроцессорлық техникада жүйені тестілеу мәселелері

Бастапқы мәліметтер жоқ

Әдебиет:

1. Б. С. Есмағамбетов. «Цифрлық құрылғылар және микропроцессорлар» пәні бойынша әдістемелік нұсқау

2. Есмағамбетов Б. С. Цифрлық құрылғылары және микропроцессорлар. Оқу құралы. Шымкент: «Нұрлы бейне» баспасы, 2010, 184с

3. Есмағамбетов Б. С. Басқару жүйелердргі микропро-цессорлық кешендер. Оқу құралы. Шымкент: «Әлем баспасы», 2013, 236с

Тапсырманың берілген күні , жұмысты қорғалған күні

Жұмыстың жетекшісі:

(аты - жөні, қолы)

Тапсырманы орындауға қабылдаған

(күні, студенттің қолы)

Ф. 7. 04-06

Қазақстан республикасы білім және ғылым министрлігі

М. О. Әуезов атындағы Оңтүстік Қазақстан мемлекеттік университеті

«Ақпараттық технологиялар және энергетика» жоғары мектебі

«Автоматтандыру, телекоммуникация және басқару» кафедрасы

«Бекітемін»

Кафедра меңгерушісі

Исмаилов С. Ө. т. ғ. к., доцент

«»2015ж.

Курстық жұмыс қорғау

Хаттамасы № 15

пәні: «Цифрлық құрылғылар және микропроцессорлар»

студент тобы -

(аты - жөні)

Курстық жұмыс тақырыбы Микропроцессорлық техникада жүйені тестілеу мәселелері

Қорғау кезінде келесі сұрақтарға жауап алынды:

Курстық жұмысты орындау кезінде алынған балл (60 мүмкіндіктен) , қорғау бағаланды (40 мүмкіндіктен ) балл.

Сомалық баллы

Жұмыстың бағасы

Курстық жұмыстың жетекшісі

Комиссия мүшелері

Комиссия мүшелері

Қорғау күні 2015ж.

Аннотация

Соңғы кезде өндірістік технологиялық процестерінде қолданылатын машиналар мен жабдықтардың көбісінде басқару әрекеттері цифрлық аппаратурамен жүзеге асады. Басқаруды бір мақсатқа бағытталған ақпараттың өзгеруі деп қарастырғанда, мұндай аппаратура микропроцессордың ақпарат өңдейтін мүмкіндігін пайдаланады. Осы тұрғыдан қарағанда, курстық жұмысында қарастырылған мәселелер RISC архитектуралы микроконтроллерлермен танысуға жол ашады.

Курстық жұмысында RISC біркристалды микроконтроллерлер архитектурасы, PIC микроконтроллерлер және AVR микроконтроллерлелдің архитектурасымен сипаттамалары қарастырылған.

Көлемі 32 бет, 12 сурет, 7 әдебиет қолданылған.

Мазмұны

Нормативтік сілтемелер 6

Пайданылатын қысқартулар мен белгілер 7

Кіріспе 8

1. Жүйені тестілеудің мәселелері 9

2. Микросхемаларды тестілеудің мәселелері 113. Логикалық талдағыштар 21

4. Сигнатуралық талдау 26

Нормативті сілтемелерПайдаланылған әдебиеттері 32

Қолданылған қысқартулар мен белгілер

МП - микропроцессор

ЭЕМ - электронды есептеу машина

ТЕСҚ - тұрақты есте сақтағыш құрылғы

ОЕСҚ - оперативті есте сақтағыш құрылғы

АЦТ - аналогты -цифрлық түрлендіргіш

БМК - біркристалды микроконтроллер

НАА - номерді автоматты анықтағыш

ЕИМ - ендік-импульстік модуляция

ҮИС - үлкен интегралды схемаларда

ОП - орталық процессор

Кіріспе

Тақырыбының өзектілігі .

Курстық жұмыстың өзектілігі тақырыб бойынша қарастылылған мателиалдардың микропроцессорлық техникада пайдалуымен анықталады.

Курстық жұмыстың мақсаттары мен міндеттері микропроцессорлық техникадағы пайдаланатын құрылғыларды қолдану принциптеріне негізделеді.

Практикалық қажеттілігі.

Курстық жұмыстың практикалық қажеттілігі қарастырылған принциетері, құрылымдық схемалары, сипаттамалары әр-түрлі цифрлық техникада қолдану мұмкіндіктерімен анықталады.

Курстық жұмыстың мазмұны тапсырманың және әдістемелік нұсқаудың талаптарына сәйкеседі [1] .

1 Жүйені тестілеудің мәселелері

Сандық есептеуіш жүйелері жарамсыздықты іздестіруде белгілі бір мәселе қойып отыр. Басқа да электронды жүйелердегідей, есептеуіш жүйелерінің компоненттері де әр түрлі себептермен жарамсыз болады, ол жүйенің жарым-жартылай немесе толығымен істен шығуына алып келеді. Есептеуіш жүйелердің архитектурасы жарамсыз компонентті іздестіруды күрделі және ұзақ процедураға алып келеді [2] .

Есептеуіш жүйелері компоненттерінің көп бөлігі үлкен интегралды схемаларда (ҮИС) іске асырылған, осы себептен есептеуіш жүйелерінің аяқталған қосымша жүйелері дайын блок түрінде қойылады. Осындай блоктың мысалы ретінде микропроцессордың өзі қызмет етеді. Кез келген ҮИС қойылғанға дейін тек шектелген тестілеуге ғана түседі. Осы тестілеу процессінде қолданылмаған сигналдар комбинациялар эксплуатация кезінде шығуы мүмкін, немесе микросхеманың сипаттағы емес тәртібін болдыратын компоненттің кейбір параметрінің өзгеруі болу мұмкін. Осы себептен ҮИС жарамсыздығы пайда болу мүмкін.

Есептеуіш жүйелердің дұрыс жұмысы үшін жарамды аппараттық құралдары және қатесіз бағдарламалық қамтамасыздандыру қажет. Кейде бұл ондай емес, және толығымен жұмыс жағдайындағы болып есептелетін бағдарламалар кейбір жағдайларда дұрыс емес нәтижені көрсетуі мүмкін. Бағдарламалар нақты тестілеу кезінде дұрыс жұмыс жасауы мүмкін, бірақ өңдей алмайтын кодтың болжамсыз жиынтығын алуы себебінен эксплуатация кезінде бұзылу мүмкін.

Мұндай бұзылудың түрінен басқа да бүлінулер бар, олар эксплуатацияның бірнеше уақыттан кейін жүйеде пайда болады. Жалпы жағдайда олар компоненттердің жөнделмеуі салдарынан болатын электрлік бүлінулерден немесе жадында сақталатын командалардың кодылар тозуынан болатын бағдарламалар келіспеушілігінен болады.

Есептеуіш жүйелердің жарамсыздығы пайда болғаннан кейін бірдестен келесі мәселе табылады. Егер бұзылу көрінбесе, зерттеуші бүлінуді аппараттық әдістерде жасыруы немесе бағдарламада қате екендігін шешуі керек. Мұндай сұраққа жауап беру оңай емес, себебі бүліну мінездемесі қарапайым диагностикалық тесттің орындалуына кедергі жасау мүмкін. Микропроцессордың басқару шинасындағы бүліну кез келген бағдарламаның орындалуына кедергі жасайды, ал операциялық жүйедегі бүліну кез келген тест-бағдарламаны ендіруді және орындалуын болдырмайды.

Шағын жүйелерде (микроконтроллерде) тест бағдарламаның жиынтығының қолмен қосу түріндегі, қолданбалы бағдарламалар секілді адрестік кеңістікте жұмыс істейтын, қарапайым әдістер жиі бүлінуді табады. Егер тест-бағдарламалар жұмыс істемесе, бүліну орны аппараттық әдістерде бар. Осындай кезде жүйеге бірнеше әдіс арқылы тест-ТЕСҚ ендіру болады. Қарапайым нұсқа ретінде жүйелік ТЕСҚ алып тастау керек және оның орынына (сокет) тест-ТЕСҚ орнату керек. Мұндай жағдайда жұмыс режімінде де істейтін жүйенің аппараттық әдістері қолданылады, мысалы орталық процессор мен жүйелік ТЕСҚ панелі арасын байланыстыру линиялар. Тағы бір әдісі ретінде - тест-ТЕСҚ жүйенің ішіне салу, ал жүйені тестілеуі кезінде жүйелік ТЕСҚ-ны рұқсат беру сигналы арқылы тумблермен тест-ТЕСҚ-на ауыстыру. Әрине, бақылау әдістерің жүйеге туралауының басқа да нұсқалары бар.

Уақыттың кез келген сәтінде микропроцессорлық жүйенің толық жағдайы көптеген линияда сигналдардың деңгейлерімен анықталады. Ағымдағы адрес адрес шиналарының параллельді линияларының жағдайымен ұсынылады. Сонымен қатар осы адрес бойынша оқылып немесе жазылып жатқан берілгендер, берілгендер шинасының параллельді линиясындағы екілік код болып табылады. Орындалып жатқан операцияның түрін анықтау үшін басқару шинасының бірнеше линиялардың жағдайын білу қажет. Сондықтан, тасымалдау туралы барлық ақпаратты алу үшін көптеген линиялардың жағдайлары белгілі болу керек. Кез келген ақпараттың «бөлігі» шинада уақыттың қысқа интервалында ғана болады. Мысалы, берілгендер жадынан оқылатын байт берілгендер шинасына жүйелік синхронизация бір периоды ұзақтығымен орналасады (мысалы, 250 нс) .

Микрокомпьютерде ақпарат параллельді кодпен уақыт бойынша тізбктік түрде жіберіледі, сондықтан ақпараттың әрбір «бөлігі» жүйеде қысқа ғана уақытта болады, содан кейін басқасымен алмастырылады. Қарапайым басқару-өлшеу құралдары, мысалы осциллограф, мұндай формада келтірілген ақпараттың индикациясына және қабылдануына есептелмеген, сондықтан жүйеде берілгендерді белгілейтін және анықтайтын арнайы құралдар қажет болады.

ҮИС, әсіресе микропроцессорлардың, корпустарының өлшемдеріне шектеулер корпустарында сигналдардың барлығы үшін сыртқы шығыстары жетіспеуіне алып келеді. Сонымен қатар, кейбір шығыстарды бірнеше функция үшін қолдануы қажет, ол сигналдардың уақыты бойынша бөлінуіне (мультиплекстенуі) қажеттілігін тудырады.

Шинаның мультиплекстенуі тестілеуді қиындата түседі, себебі кез келген уақытта мультиплекстенетін линияда қандай ақпараттың орналасқанын шешу керек. Сонымен, қарапайым басқару-өлшеу құралдары мұндай линияларда ақпаратты демультиплекстеуге бейімделмеген және арнайы құралдарды қолданудың қажеттілігі туындайды.

2. Микросхемаларды тестілеудің мәселелері

ҮИС тестілеу мәселелерін анық көрсету үшін типтік микросхеманың тестілеуіне қажет уақытты анықтаймыз. Микропроцессор секілді күрделі құралды тексеру үшін оның командалар жүйесіның әр командаға үшін қажетті тест-комбинациялар саны (әр команда үшін барлық мүмкін екілік жиынтығы) келесі формуламен анықталады [2] :

С=2 mn ,

мұнда n -берілгендердің сөз ұзындығы (бит саны), ал m - микропроцессор командалар жүйесіндегі командалардың саны.

Мысалы ретінде 76 командасы және берілгендердің 8-биттік шинасы бар 8080 микропроцессорды қарастырайық: n=8 және m =76. Микропроцессордың толық тексерілуі үшін тест-комбинацияның жалпы саны:

С=2 8*76 =2 608 .

Осы санды бізге ыңғайлы ондық жүйеге түрлендірейік:

2 608 =10 х ,

Осыдан

x=log 10 (2 608 ) = log 10 2*608=0, 30103*608=183, 02624.

Яғни, тест-комбинациның жалпы саны

С=10 183, 02624 .

Әр тест 1мкс ұзарады деп болжайық (8080 микропроцессор үшін мүмкін емес мән) . Сонда барлық тестті өткізуге 10 183, 02624 /10 6 с=10 177, 02624 с қажет. 365-күндік жылда 3, 1526*10 7 с бар. Сондықтан барлық тесттің орындалуы 10 177, 02624 /3, 1526*10 7 =0, 3171*10 170, 02624 жылдан кейін бітеді. Егер микропроцессордың тексеруін қазір бастайтын болсақ, ол 3, 171*10 169 жылдан кейін аяқталады!

Келтірілген есептеулер «күрделі сандық микросхеманы, мысалы микропроцессорды ешқашанда толығымен тексеру мүмкін емес» екендігін көрсетеді.

Осыдан байқайтынымыз, әрбір компьютер ешқашанда толық тексерілмеген және толығымен тексерілуі мүмкін емес, оны тексеру үшін шектелген командалар және екілік жиынтықтарды қолданылған. Автоматты сынаушы қондырғыларды және микросхемаларды дайындаушылар ҮИС үшін шектелген екілік тестжиынтықтар көмегімен негізгі функцияны бақылай отырып, ҮИС барлық тест-жиынтықтарда дұрыс жұмыс жасайды деп осындай бақылаудың нәтижесіне сүйене отырып осы мәселені шешеді. 16-биттік микропроцессорға өту кезінде тестілеу мәселесі одан сайын актульды болады.

Жүйелік ядро

Жүйенің жұмысқа қабілеттігін ұстап тұру үшін оның кей бір компоненттерінде бүліну болмау керек. Осы маңызды компоненттерді біріге отырып жүйелік ядро деп аталады [3] . Оған әдетте орталық процессор (ОП), синхронизацияның жүйелік генераторы, басқару шинасы және адрес шинасы жатады.

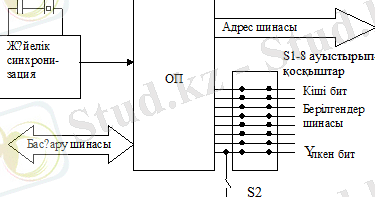

Сандық компьютерді перифериялық схемамен қоршалған ядро деп қарастыруға болады, және жүйенің басқа да компоненттерін тексеру үшін ядроның жұмысы жасап тұруы қажет. Егер ОП-ге команданы ендіру және берілгендер шинасын ажыратып тастайтын әдістері жүйеде алдын ала қарастырылған болса, жүйелік ядроны тексеру оңай. Әдетте ОП-ге бос команданың қандай-да бір түрі ендіріледі, мысалы NOP немесе MOV A, A. Берілгендер шинасын ОП-дан берілгендер шинасынан ажырататын «тайғанақты» ауыстырып-қосқыштар көмегімен ажыратуға болады. ОП-ге ендірілетін бірбайтты команда тесттік ауыстырып-қосқыштар жағдайымен анықталады, олардың көмегімен ОП-ге баратын берілгендер линиясының жағдайын белгілеуге болады. Осыдан кейін жүйелік ядроны ЕРІКТІ ЕСЕП режіміне аударуға болады. 1 суретте көрсетілген S 1 символымен белгіленетін сегіз «тайғанақты» ауыстырып-қосқыштар ОП-ды берілгендер шинасынан ажыратуға мүмкіндік береді.

Сурет 1. Жүйелік ядро

S 2 ауыстырып-қосқышы үлкен линияны жерге тұйықтайды, сондықтан ОП жадтың кез келген ұяшығынан он алтылық 7F кодыны оқиды. Көрсетілген схеманы 8080, 8085 және Z80 микропроцессорларында ерікті есепті болдыруға қолданылады.

S 1 көмегімен берілгендер шинасы ажыратылғанда және S 2 жерге тұйықталған кезде, ОП келесі команданы таңдау үшін жадтан оқу операциясын іске асырады. Осы команда NOP типті команда ретінде әрқашанда түсіндіріледі. Осы себебтен ОП жадтың келесі адресіне өтеді және оқудың тағы бір операциясын ұйымдастырады. ОП жадтың әр ұяшығынан «операция жоқ» командасын оқып тұрады, нәтижесінде адрес шинасында барлық мүмкін екілік код құралады. Адрес шинасының әр линиясындағы сигналдарды қарастырған кезде қорек көзіне немесе жерге тұйықталғанын, линияның бұзылғанын немесе адрес шинасының басқа линиясына тұйықталғанын анықтауға болады.

Егер адрес шинасының линиясы бойынша дұрыс сигналдар берілетін болса, жүйелік ядро жұмысты дұрыс атқарады деп есептеуге болады. Басқару шинасының линиялардың жарамсыздығы немесе синхронизацияның жүйелік генераторында бұзылуы бос есеп режимінде дұрыс жұмыс жасауын болдырмайды және қызмет көрсету персоналдарының жүйелік ядроның әр түрлі бөліктерін зерттеуге мәжбүр етеді. Бос есеп тесті кез келген микропроцессорға қолдануға болады, және микропроцессорлық жүйенің кейбір маңызды компоненттерін тестілеудің қарапайым әдістерін қамтамасыз етеді. Бос есеп режимінің төмендегі бөлімде қарастырылатын сигнатурлық талдау үшін үлкен мағынасы да бар.

Орталық процессорды тестілеу

Жүйеде ең күрделі компоненттерінің бірі бола отырып микропроцессор ең сенімдісі де екен. Айтылып өткендей, микропроцессор секілді күрделі ҮИС толығымен тексеру мүмкін емес, оның микросхемалардың функционалды тестілеуді өткізуге болады. Мұндай тестілеуде әр функция шектелген екілік жиынтықтың көптігі арқылы тексеріледі [4] .

Эксплуатация кезінде ОП тестілеуінің қарапайым түрі - жүйенің бос есеп режіміне аударуы. Ол ОП берілгендер шинасынан команданы дұрыс оқитынын, адрес шинасында адрестік жиынтықты қалыптастыратынын және жүйелік синхронизацияның сигналына дұрыс қарайтынын көрсетеді. Жүйелік шинаның линиясындағы, мысалы R/W линиясында, сигналдарды бақылай отырып басқару шинасын жарым-жартылай тексеруге болады.

Әдетте ОП эксплуатация кезінде жұмысқа жарамды деп саналады, және жүйенің бос есеп режиміне аударуынан басқа ол үшін арнайы тексеруді өндірілмейді. Әрқашанда ОП тест-бағдарламаларды орындау мүмкіндігі бар деп есептеледі.

Жарамсыз болған ОП өзін-өзі тексере алмайды. Осындай жағдайда тек ОП тексеруі үшін жүйеге екінші ОП қосылу мүмкін. Көрініп тұрғандай, екінші ОП пайда болуымен жүйенің жалпы күрделілігі кенет өседі, осыдан оның сенімділігі нашарланады. Бұл тәсіл өте сирек қолданылады, үйткені екінші ОП схемаларын тестілеу қажет. Сонда да, күрделі бақылау-өлшеу құралдарының көбісінде микропроцессорлық жүйені тексеру үшін өздерінің ендірілген микропроцессорлары бар.

Тұрақты есте сақтау құрылғыны тестілеу

Тұрақты есте сақтау құрылғы термині (ТЕСҚ) бағдарламаларды ендіру әдістерімен ерекшеленетін (олардың бағдарламалауының әдістерімен) микросхемалардың бірнеше түрлеріне қатысты. Атауы айтып тұрғандай, Бағдарламаның қарапайым орындалуы кезінде ТЕСҚ тек қана оқылуы ғана мүмкін, ал оларға жазу мүмкін емес, яғні сақталып жатқан бағдарламаларды өзгерту мүмкін болмайды.

ТЕСҚ микросхемасының көбі бағдарламаның орындалуы кезінде өзгермейтін белгіленген командаларды сақтайды. Осы себебтен микросхемасының ішіндегісін бақылауды ұйымдастыруға мүмкіндік бар. ТЕСҚ микросхемасында тек 06 және 07 екі оналтылық саны сақталады деп есептейік. Осы сандардың қосылуы микросхемасының соңғы ұяшығында болатын оналтылық 0D нәтижені береді. Тексеру барысында ТЕСҚ соңғы ұяшығынан басқа құрамын барлығын қосатын бағдарлама орындалады, содан соң өзінің нәтижесін соңғы ұяшықтағымен салыстырады. Егер екі сан бірдей болса, ТЕСҚ құрамы дұрыс саналады, ал егер әр түрлі болған жағдайда ТЕСҚ бұзылу туды деп қорытынды жасауға болады. Бұл сан CHECKSUM бақылау суммасы деп аталады, ал қарастырылған әдіс тіркелген сақталу ақпараты бар ТЕСҚ микросхеманы қарапайым және эффективті тексеруді қамтамасыз етеді.

Соңғы ұяшықтан басқа құрамының барлығын қосу кезіндегі толып кетуіне назар салмау болса, CHECKSUM әдісі кез келген сыйымдылықты микросхемаларда қолданылады [3] . Мысалы ТЕСҚ үш 16-лық сандар 7С, 20 және 8А болатын болса, олардың қосылуының нәтижесі екібайттық 126 сан болады. Егер ТЕСҚ әр ұяшығы байт түрінде болатын болса, CHECKSUM ретінде нәтижесінің 26 кіші бөлігі ғана есте қалады. Тест-бағдарлама бақылау суммасын сақталған 26 мәнімен салыстырады.

Бағдарлама жүйеде бірнеше ТЕСҚ микросхемаларда сақталса, бірінші ТЕСҚ микросхеманың соңғы команда шартсыз өту болу керек. Ол бақылау суммасы бар соңғы ұяшығын айналып өтеді. Сондай ақ, әр микросхемада соңғы ұяшықты айналып өту үшін шартсыз өтудің командалары болу керек.

Әдетте бақылау қосындысының тест-бағдарламасы ТЕСҚ -ың жүйелік тестін. Жүйелік тест есептеу жүйесінің қосылуынан кейін бірдестен жұмыс жасай бастайды. Идеалды жағдайда ТЕСҚ-ың тесті өзін-өзі де тексеруі керек.

Оперативті есте сақтау құрылғыларды тестілеу

Оперативті есте сақтау құрылғылар (ОЕСҚ) микросхемаларда бағдарламаның орындалуы кезінде оқу және жазу операциялар іске асыралады. ОЕСҚ микросхемаларын тексеру үшін берілгендерді әр ұяшыққа жазу қажет, ал содан кейін оларды санау керек. Егер ұяшықтан саналған екілік код жазылғанмен сәйкес болса, ұяшық жарамды болады. Әдетте тексеру үшін 01010101 (55 16 ) және 10101010 (АА 16 ) ШАХМАТТЫ ТАҚТА деп аталатын жинақтары қолданылады [5] .

ШАХМАТТЫ ТАҚТА тесті қорек көзі қосылғаннан кейін ОЕСҚ-ны тексеру үшін қолданылады. Тест-бағдарлама шахматты тақтаны минималды адресінен бастап ОЕСҚ-ың әр ұяшықтарына жазады.

Көп жағдайда 55 және АА тест-жинақтардың орнына қарапайым 00 және FF тест-жинақтары қолданылады. Шахматты тақталар жинақтары ОЕСҚ микросхемаларының бастапқы тексеруінің қарапайым әдісі ретінде қолданылғанымен, олар ескірген тест болып саналмайды. ОЕСҚ жарамсыздығын табу үшін жүйені тексеру кезінде «адымдағыш бірліктер» деген одан да қатқыл тест іске қосылады. Бұл тестте ОЕСҚ әр ұяшығына мынандай екілік тізбектері жазылады және содан соң оқылады:

Мұндай тест берілгендердің көрші линияларда айқасты бағытталған бөгеттерге кез келген сезімділікті табуға арналған. Богеттер тексеріліп жатқан ұяшықтан 1-ді саналу кезінде екі көрші разрядтарда табылу мұмкін.

ОЕСҚ микросхемадағы берілгендер мен адрес туралы алып жүретін линиялар бір біріне жақын орналасқан. Осы себептен, ішкі топология «жиынтыққа сезімділік» эффектісін тудыруы мүмкін. Бұл эффектте нақтылы екілік код басқа да берілгендер және адрес линияларына жиірікте шахматты кодпен анықталмайтын кернеуды бағыттау мүмкін. Бірақ, бағытталған кернеуге сезімді микросхемалар әдетте әзірлеу кезінде немесе өндіріс процесінде таңдаулы бақылау кезінде айқындалуы мүмкін.

... жалғасы- Іс жүргізу

- Автоматтандыру, Техника

- Алғашқы әскери дайындық

- Астрономия

- Ауыл шаруашылығы

- Банк ісі

- Бизнесті бағалау

- Биология

- Бухгалтерлік іс

- Валеология

- Ветеринария

- География

- Геология, Геофизика, Геодезия

- Дін

- Ет, сүт, шарап өнімдері

- Жалпы тарих

- Жер кадастрі, Жылжымайтын мүлік

- Журналистика

- Информатика

- Кеден ісі

- Маркетинг

- Математика, Геометрия

- Медицина

- Мемлекеттік басқару

- Менеджмент

- Мұнай, Газ

- Мұрағат ісі

- Мәдениеттану

- ОБЖ (Основы безопасности жизнедеятельности)

- Педагогика

- Полиграфия

- Психология

- Салық

- Саясаттану

- Сақтандыру

- Сертификаттау, стандарттау

- Социология, Демография

- Спорт

- Статистика

- Тілтану, Филология

- Тарихи тұлғалар

- Тау-кен ісі

- Транспорт

- Туризм

- Физика

- Философия

- Халықаралық қатынастар

- Химия

- Экология, Қоршаған ортаны қорғау

- Экономика

- Экономикалық география

- Электротехника

- Қазақстан тарихы

- Қаржы

- Құрылыс

- Құқық, Криминалистика

- Әдебиет

- Өнер, музыка

- Өнеркәсіп, Өндіріс

Қазақ тілінде жазылған рефераттар, курстық жұмыстар, дипломдық жұмыстар бойынша біздің қор #1 болып табылады.

Ақпарат

Қосымша

Email: info@stud.kz