Intel P6 процессорының архитектурасы мен жұмыс режимдері және AND және XLAT командаларының эмуляциясы

Жұмыс түрі: Курстық жұмыс

Тегін: Антиплагиат

Көлемі: 25 бет

Таңдаулыға:

Мазмұны.

Мазмұны. 1

Кiрiспе 2

1. Тапсырма 3

2. Программаның сипаттамасы 3

2. 1. Жалпы мағлұматтар 3

2. 2. Программада қолданылған процедуралар 3

3. Командалар конвеерiн үйымдастыру 4

4. Процессордың жұмыс iстеу режимi және жадыны үйлестiру 7

5. Ішкі құрсым-жады 9

6. Жалпы мақсатты регистрлер 11

7. Сегменттік регистрлер 12

8. Логикалық AND 14

9. XLAT байттарды түрлендіру. 15

Қорытынды 16

Қолданылған әдебиеттер 17

А-Қосымшасы 18

Программа листингiсi 18

Кiрiспе

60-шы жылдардағы интегралды схемалардың жасалуына байланысты шағын процессорлардың пайда болуына әкеп соқты. Интегралды схемалар өз бойына әр түрлi электронды компоненттердi силиконда “чипте” жиналды. Интегралды схемаларды жасаушылар осы кiшкене чиптi, қырық аяқты жәндiкке ұқсаған функционалды жүйеге салды. Ал 70-шi жылдардың басында Intel 8008 процессордағы шағын компьютерлер шағын процессорлардың бiрiншi буынын әлемге шығарды.

1974 жылдары intel 8080 екiншi буынды шағын процессорлар шықты. Осы жетiстiк басқа кәсiпорындарды ұқсастырған процессорлады шығаруға ниет бердi.

1978 жылы Intel фирмасы үшiншi буынды шағын процессорларды Intel 8086 шығарды. Ол 8080 процессорымен сәйкес болды, және осы үшiншi буынның шығуы осы бағытта көп алға, басқанын көрсеттi.

1. Тапсырма

AND және XLAT командаларын орындау кезiндегi, P6 шағын микропроцессордың өзгерiстерiн және мәлiметтердiң жылжуын бақылау және көрсету. Регистрлердiң бөлiнуi, команданың кiшкене микрокомандаларға бөлiнуi және команда адрестерiнiң калыптасуын эмуляциялық программа ретiнде бақылап отыру.

2. Программаның сипаттамасы

2. 1. Жалпы мағлұматтар

Программа WINDOWS - қа арналған жоғары деңгейлi Delphi тiлiнде жазылған. Ол программаны жiберу үшiн KUAT. EXE файлын жандандыру арқылы iске қосады.

Жүйелiк қажеттiлiктер: Программаны iске қосу үшiн P II 200 MHz процессоры, 2 Mb Жедел жадысы, 3Mb дискiлiк орын және 1024*768 пикселдi, диагоналi 15 болатын монитор қажет.

2. 2. Программада қолданылған процедуралар

TForm1. FormCreate(Sender: TObject) процедурасы форманың экранда салыну кезiнде “к” айнымалысын нөлге теңестiредi. Ол айнымалы процессордағы команда орындалу импульстерiн санау үшiн қажет. Өйткенi әрбiр команда үшiн импульстар саны әртүрлi болып келедi.

TForm1. BitBtn2Click(Sender: TObject) процедурасы “к” айнымалысының мәнiн оқып шағын процессордың маған берiлген командаларға байланысты күйiн оқып, келесi күйге ауыстырады. Және бiр команданың импульс сандары бiткен соң, шағын процессор келесi команданы орындау үшiн дайындаладық күйге ауысады.

TForm1. BitBtn1Click(Sender: TObject) процедурасы программаны аяқтағаннан соң, программадан шығу операциясын орындайды.

3. Командалар конвеерiн үйымдастыру

Р6 процессорлардың жалпы құрылымы 1 суретте көрсетілген. Гарвардтық ішкі құрылым командалар және мәліметтер ағындарының бөлінуі негізінде жасалған. Бұл командалар және мәліметтер ағындары жүйелік шинадан шығып, сыртқы интерфейс блогы арқылы процессордың кристаллында орналасқан бөлек командалар құрсым-жадыға және мәліметтер құрсым-жадыға келіп түседі (бірінші деңгейлі құрсым-жады L1) .

Ішкі интерфейс блогы процессордың жүйелік шинамен және екінші деңгейлі құрсым-жады шинасымен (L2) алмасуының хаттамасын іске асырады. Жүйелік шинаға енгізу-шығару контроллері, жады, жүйенің басқа активті құрылғылары қосылады. Ал екінші деңгейлі құрсым-жады шинасы микропроцессормен бірге жалпы корпуста орналасқан бөлек микросхема түрінде жасалған.

Бірінші деңгейлі сыйымдылықтары 16 Кбайттан тұратын командаларды және мәліметтерді орналастыруға арналған. Оларға қатынау жиілігі процессордың тактілік жиілігіне сәйкес (жүздеген МГц) . Осыған байланысты процессордың өнімділігі өте жоғары болады. Себебі сыртқы жадыға қатынау саны қысқарады. Ал сыртқы жадыға қатынау жиілігі жүйелік шинаның мүмкіндіктерімен анықталады (ондаған МГц) .

Р6 процессорларында екінші деңгейлі құрсым-жады (L2) бар, оның сыйымдылығы 256 Кбайт, 512 Кбайт немесе 1Мбайт болуы мүмкін, ол бөлек кристаллда жасалынады да, процессормен бірге бөлек корпуста орналасады. Оның қолданылуы өнімділікті қосымша жоғарлатуға мүмкіндік береді.

Процессордағы декодерлеуді таңдау блогы командалар құрсым-жадысынан 32 байт командалар кодын (ұзындығы 256 бит құрсым жадының жолы) таңдайды да, содан кейін командалардың бөлінуін және декодерленуін орындайды. Таңдалған командалар орындауға бір микрооперацияны қажет ететін қарапайым командалар және бірнеше микрооперацияны қажет ететін күрделі командалар болып екіге бөлінеді.

Қарапайым командаларға, мысалы, қосу командасы, азайту командасы, салыстыру командасы, логикалық операциялар және операндтарды регистрлік адрестеуді қолданатын бірқатар командаларды жатқызуға болады. Осы командалардың декодерлеуін сәйкес микрокомандаларды қалыптастыратын DC1, DC2 декодерлері жүзеге асырады.

DC3 декодері орындау үшін төртке дейін микрооперацияларды қажет ететін күрделі командаларды орындайды. Сәйкес микрокомандалар осы декодердің шығысында қалыптасады. Сонымен декодерлеуді таңдау блогы микрокомандалардың алты ағынын қалыптастырады және олар программаның үш командасының параллельді орындалуын қамтамасыз етеді.

Егер командалар ағынында шартты өту командасы кездессе онда тармақталуды болжау блогы қосылады. Ол, өтудің шарты анықталғанға дейін келесі таңдалған команданың адресін қалыптастырады.

Өтудің адресін болжау тетігі (механизмі) төменде сипатталған.

Микрокомандалар ағыны қалыптасқаннан кейін декодерленген командалардың орындалуына қажетті регистрлер бөлінеді. Бұл процедураны регистрлерді үлестіру блогы (RAT - Register Alias Table) жүзеге асырады. Ол командада көрсетілген әр логикалық регитр үшін алмасу регистрлер блогына (RRF - Reterement Register File) кіретін 40 физикалық регистрлердің біреуін бөліп береді. Бұл процедура бірдей логикалық регистрлерді қолданатын командаларды бір уақытта немесе олардың тізімін өзгертіп орындауға мүмкіндік береді.

1 сурет. Р6 процессорлардың жалпы құрылымы

Декодерленген командалар ағынын тиімдірек орындау үшін, командалар тізімін өзгертуге мүмкіндік беретін блок (ROB - Re-Order Buffer) қолданылады. Бұл блок буфер түрінде құрылған, оған декодерленген командалардың орындалуын қамтамасыз ететін микрокомандалар келіп түседі. Буферде бір уақытта 40 микрокоманда бола алады, олар RRF регистрлер блогынан немесе жадыдан таңдалынатын операндтардың дайын болғанына қарай, орындаушы құрылғыларға жіберіледі. Командалар келіп түскен ретпен емес, сәйкес операндтардың және орындаушы құрылғылардың дайын болғанына қарай орындалады. Нәтижесінде кейінірек келіп түскен командалар алдындағы командалардан бұрын орындалуы мүмкін. Сонымен командалардың орындалу реті бұзылады, нәтижесінде параллельлі істеп жатқан орындаушы құрылғылар толығымен жүктеледі де, процессордың өнімділігі артады.

Микрокомандалар орындаушы құрылғыларға үлестіру блогы (RS - Reservation Station) арқылы келіп түседі. Бұл блок микрокоманданы сәйкес орындаушы құрылғыға, ол босаған сәтте жібереді. Үлестіру блогы бес шығыс порттан тұрады және ол үш команданың бір уақытта орындалуын қамтамасыз етеді.

IU1, IU2 (IU - Integer Unit) атқарушы блоктар бүтін сандық операндтарды өңдейді, FPU (Floating - Point Unit) блогы жылжымалы үтірлі сандармен орындалатын операцияларды орындайды, MMX блогы бір уақытта бірнеше упакованные* символдардың өңдеуін қамтамасыз етеді, SSE блогы жылжымалы үтірлі сандардың ағынымен орындалатын операцияларды орындайды.

4. Процессордың жұмыс iстеу режимi және жадыны үйлестiру

Р6 процессорлар, алғашқы Intel 80286, 80386, 80486 шағын процессорлары сияқты негiзгi үш функционалды режимi бар:

- нақты адрестер режимi (нақты режим),

- қорғалған виртуалды адрес режимi (қорғалған режим),

- жүйелiк басқару режимi.

Нақты режимде Р6 процессоры өте тез жұмыс iстеетiн 8086 шағын процессоры сияқты iстейдi, яғни 16 разрядты операндтарды және 1 мегабайт адрестейтiн жедел жадысын өңдейдi. Осымен қатар процессор Р6 буынына енген кеңейтiлген командаларды орындайды.

Қорғалған режимде бiр уақытта бiрнеше программа орындалуы мүмкiн, бiрақ олар бiр бiрiнен процессордың операциялық жүйесiмен қорғалады. Арнайы механизм арқылы программалар ауысып отырады. Осы режимде Р6 процессоры 8086 шағын процессоры үшiн жазылған программыны орындау мүмкiн, егер қорғалған режимнiң модификациясы виртуалды 8086 режимi орындалатын болса. Виртуалды 8086 режимiнде процессор 20 разрядты адрестi қалыптастырады. Қажет болған жағдайларда, осы режимде парақталған жедыны және жүйелiк программаларды қорғауды қамтамасыз етiп отырады.

OSFXCR бiрге тең болған жағдайында FXSAVE/FXSTOR командаларын орындауға рұқсат бередi, ол командалар FPU, MMX, SSE блоктарының күйiн сақтау/қалпына келтiру үшiн қолданылады.

GDTR, IDTR, LDTR, TR жүйелiк адрестер регистрi сегмент таблицасына қатынас жасау үшiн қажет. Олар арқылы қорғаныс режимiнде жадының адрестеуi орындалады:

- GDT глобалды дескриптор таблицасы

- IDT үзулер дескрипторының таблицасы

- LDT локалды дескриптор таблицасы

- TSS тапсырмалар күйiнiң сегментi

GDTR глобалды дескриптор регистр таблицасы және IDTR үзулер десприпторының регистр таблицасы GDT және IDT базалық 32 разрядты адрестi және 16 разрядты көлемдi таблицаларын өз құрамына енгiзедi. LDTR локалды дескриптор регситр таблицасына және TR тапсырма регистрiне 16 разрядты селектор енедi, ол LDT таблицасына және TSS сегментiне қатынауды рұқсат етедi, және әр тапсырма үшiн анықталады. Осылардың әрқайсысымен программды қатынаспайтын дескриптор сегментiнiң регистрi байланыс ұстайды.

5. Ішкі құрсым-жады

Құрсым жады процессор мен негізгі жады арасында орналасқан, шапшаң әрекетті шектеулі көлемді буферлік жады болып табылады. Жұмыс процесінде информацияның бөлек блоктары негізгі жадыдан құрсым-жадыға көшіріледі. Негізгі жадыдан құрсым-жадыға информацияны жуктеу процедурасы құрсымлеу деп аталады. Процессор командаға немесе мәліметтерге қатынағанда алдымен олардың құрсым-жадыда бар екенін тексереді. Егер керек информация сол жерде болса, онда ол тез алынады, себебі құрсым-жадыға қатынау процессордың тактілік жиілігімен орындалады. Қатынаудың осы түрін құрсым-дәл түсу (кэш-попадание) деп аталады. Егер керек информация құрсым-жадыда болмаса, онда ол негізгі жадыдан алынады және сол сәтте құрсым-жадыға жазылады. Қатынаудың осы түрін құрсым-қате түсу (кэш-промах) деп аталады.

Егер құрсым-дәл түсу құрсым-қате түсуге қарағанда неғұрлым көп жүзеге асырылса соғұрлым есептеу жүйенің шапшаңдығы өседі.

Р6 процессорларда командаларды және мәліметтерді сақтауға арналған ішкі құрсым жады қолданылады. Олардың әрқайсысының көлемі 16 Кбайт.

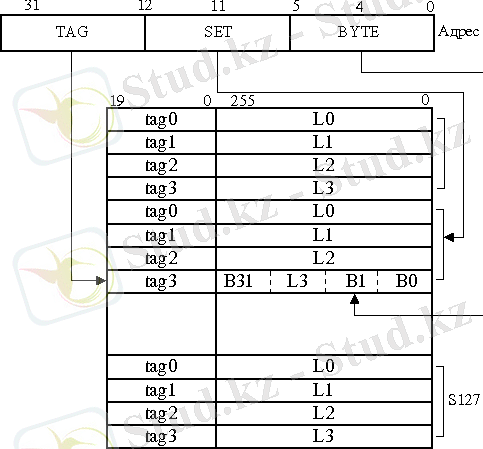

Ішкі құрсым жадыдан басқа қосымша сыртқы құрсым-жады бар. Оған қатынау үшін сыртқы интерфейс блогына қосылатын, процессордың тактілік жиілігімен жұмыс істейтін бөлек шина қолданылады. Құрсым жадының құрылымы 2-ші суретте көрсетілген. Бұл жады ассоциативті типті, ұзындығы 32 байт жолдардан тұрады. Командалар бүрекме-жадыда жолдар 128 жинаққа біріктірілген S0 - S127 және олардың әрқайсысы 4 жолдан (L0, L1, L2, L3) тұрады. Мәліметтердің құрсым-жадысы екі жолы (L0, L1) бар 256 S0 - S255 жинақтан тұрады.

2 сурет. Құрсым-жадының құрылымы және оған қатынау блогы.

Құрсым-жады адрестеуі адрестің 32 разряды көмегімен орындалады, олар 3 өріске бөлінеді: TAG, SET, BYTE.

Құрсым жадыға қатынау негізінде SET өрісінің құрамы таңдалынатын жинақтың нөмерін анықтайды. Адрестің жоғарғы разрядтарының TAG -өрісі, мәндері тегтер өрістерінің (TAG0 - TAG3) құрамымен таңдалған жинақтың жолдарында салыстырылады. Егер TAG мәні бір жолдың тегінің құрамымен сәйкес келсе, онда құрсым-дәл түсу бекітіліп, BYTEөрісі адрестеген, операнд осы жолдан алынады. Егер TAG мәні бір жолдың тегінің құрамымен сәйкес келмесе, онда құрсым-қате түсу бекітіледі.

Құрсым-жады мен негізгі жады арасында жолдарды қайта жіберуді сыртқы интерфейс блогы дестелі циклдар көмегімен орындайды. Дестелі циклдарды және 64-разрядты жүйелік шинаны қолдану құрсым-жадының құрамын тез жаңартуын қамтамасыз етеді.

6. Жалпы мақсатты регистрлер

... жалғасы- Іс жүргізу

- Автоматтандыру, Техника

- Алғашқы әскери дайындық

- Астрономия

- Ауыл шаруашылығы

- Банк ісі

- Бизнесті бағалау

- Биология

- Бухгалтерлік іс

- Валеология

- Ветеринария

- География

- Геология, Геофизика, Геодезия

- Дін

- Ет, сүт, шарап өнімдері

- Жалпы тарих

- Жер кадастрі, Жылжымайтын мүлік

- Журналистика

- Информатика

- Кеден ісі

- Маркетинг

- Математика, Геометрия

- Медицина

- Мемлекеттік басқару

- Менеджмент

- Мұнай, Газ

- Мұрағат ісі

- Мәдениеттану

- ОБЖ (Основы безопасности жизнедеятельности)

- Педагогика

- Полиграфия

- Психология

- Салық

- Саясаттану

- Сақтандыру

- Сертификаттау, стандарттау

- Социология, Демография

- Спорт

- Статистика

- Тілтану, Филология

- Тарихи тұлғалар

- Тау-кен ісі

- Транспорт

- Туризм

- Физика

- Философия

- Халықаралық қатынастар

- Химия

- Экология, Қоршаған ортаны қорғау

- Экономика

- Экономикалық география

- Электротехника

- Қазақстан тарихы

- Қаржы

- Құрылыс

- Құқық, Криминалистика

- Әдебиет

- Өнер, музыка

- Өнеркәсіп, Өндіріс

Қазақ тілінде жазылған рефераттар, курстық жұмыстар, дипломдық жұмыстар бойынша біздің қор #1 болып табылады.

Ақпарат

Қосымша

Email: info@stud.kz