Intel шағынпроцессорларының құрылымы және Pentium III моделінің архитектурасы: кэш-жад, регистрлер және IDIV командасы

Жұмыс түрі: Материал

Тегін: Антиплагиат

Көлемі: 20 бет

Таңдаулыға:

Кiрiспе бөлiм

1. INTEL процессорларының құрылымы мен функциясы

Негiзiнен процессорлар Intel 80х86 шағынпроцессорлардың жалпы жолын жалғастырады. Intel фирмасының модельдерінің алдыңғы шағынпроцессорларға қарағанда бірқатар архитектуралық және құрылымдық ерекшеліктерге ие. Осы ерекшклкрдің негізгілері мыналар болып табылады: Гарвардтық құрылым - бүркеме жадының бөлек ішкі блоктарын негізгендіктен, командалар және мәліметтер ағындары бөлек сақталады, Суперскалярлық архитектура, параллельді жұмыс істеп жаьқан орындаушы құрылғыларда бір уақытта бірнеше командалардың орындалуын қамтамасыз етеді, Командалардың динамикалық орындалуы, яғни командалардың орындалу реті өзгереді ( командалардың алдын-ала орындалуы - спекулятивтік орындалу ), кеңейтілген регистрлік файлды қолдану (регистрлардің атын өзгерту), тармақталуды тиімді болжау. .

1. 1 Pentium III процессорының моделі

Кез-келген орындалатын программа шағынпроцессордың белгілі ресурстар жиынына ие болады. Бұл ресурстар программаның командалары жадыда сақталыну үшін және орындалу үшін қажет.

Процессорлардың сипаттамалары келесідей: 32- разрядты ішкі құрылым; 36 разрядты адреске және 64 разрядты мәліметке арналған жүйелік шинаны қолдану; командалар мен мәліметтерге арналған, әрқайсысының сыйымдылығы 16Кбайт болып келетін бөлек, ішкі, бірінші деңгейлі (L1) бүркеме-жады; сыйымдылығы 2Мбайтқа дейінгі екінші деңгейлі командалар мен мәліметтердің жалпы бүркеме-жадысын қолдау; командалардың конвейерлік орындалуы; жоғары дәлдікпен программалық тармақталудың бағытын болжау; жылжымалы нүктелі операциялардың жеделдетілген орындалуы; жадыға қатынау кезінде артықшылық бақылау (қорғалған режим) ; мультипроцессорлық жүйелердің жүзеге асыруын қолдау; өзіндік тестілеуді, жөндеуді және өнімділіктің мониторингісін қамтамасыз ететін ішкі құралдардың бар болуы

2. Шағын процессор құрылымы

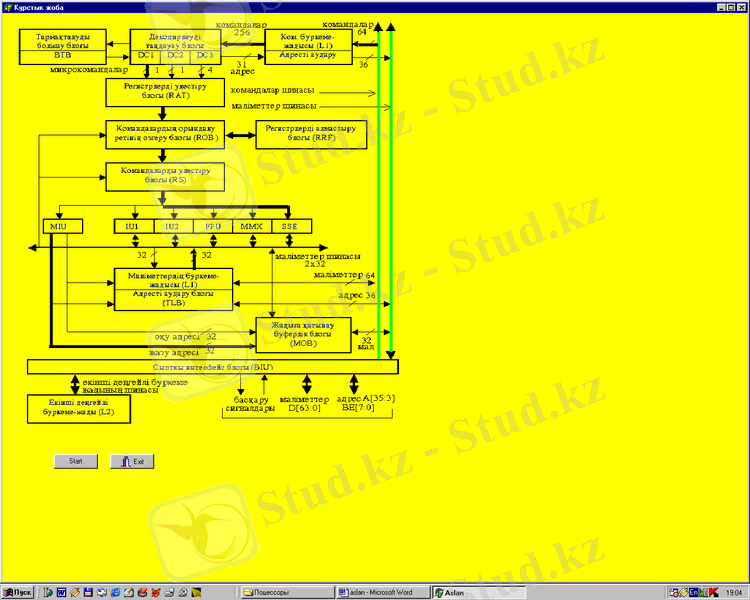

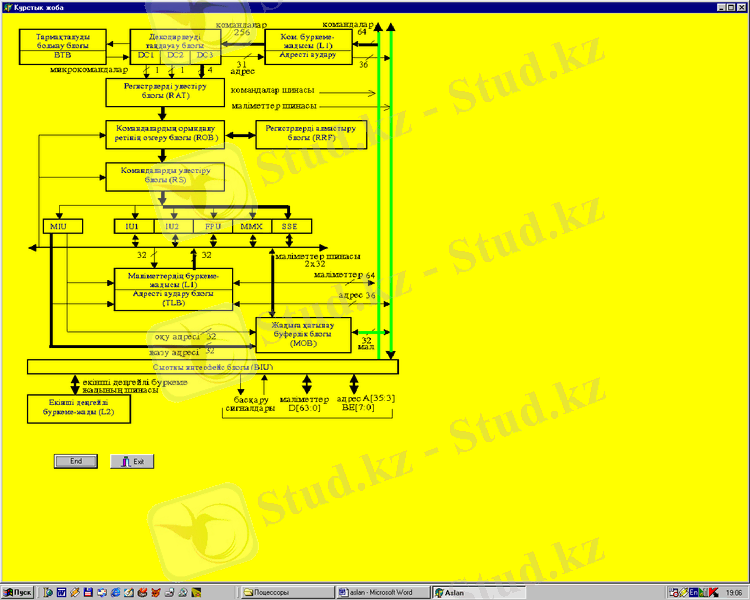

Процессорлардың жалпы құрылымы суретте көрсетілген.

Ішкі интерфейс блогы процессордың жүйелік шинамен және екінші деңгейлі бүркеме-жады шинасымен (L2) алмасуының хаттамасын іске асырады. Жүйелік шинаға енгізу-шығару контроллері, жады, жүйенің басқа активті құрылғылары қосылады. Ал екінші деңгейлі бүркеме-жады шинасы микропроцессормен бірге жалпы корпуста орналасқан бөлек микросхема түрінде жасалған. Жүйелік шинамен алмасу 64-разрядты екі бағытты мәліметтер шинасы, 41-разрядты мекен шинасы және басқару сигналдарын беруге арналған бірқатар тізбектер көмегімен жүзеге асады.

Бірінші деңгейлі сыйымдылықтары 16 Кбайттан тұратын командаларды және мәліметтерді орналастыруға арналған. Оларға қатынау жиілігі процессордың тактілік жиілігіне сәйкес (жүздеген МГц) . Осыған байланысты процессордың өнімділігі өте жоғары болады. Себебі сыртқы жадыға қатынау саны қысқарады. Ал сыртқы жадыға қатынау жиілігі жүйелік шинаның мүмкіндіктерімен анықталады (ондаған МГц) .

Қарапайым командаларға, мысалы, қосу командасы, азайту командасы, салыстыру командасы, логикалық операциялар және операндтарды регистрлік адрестеуді қолданатын бірқатар командаларды жатқызуға болады. Осы командалардың декодерлеуін сәйкес микрокомандаларды қалыптастыра

тын DC1, DC2 декодерлері жүзеге асырады.

Сурет. процессорлардың жалпы құрылымы

.

Өтудің адресін болжау тетігі (механизмі) төменде сипатталған.

Микрокомандалар ағыны қалыптасқаннан кейін декодерленген командалардың орындалуына қажетті регистрлер бөлінеді. Декодерленген командалар ағынын тиімдірек орындау үшін, командалар тізімін өзгертуге мүмкіндік беретін блок (ROB - Re-Order Buffer) қолданылады. Бұл блок буфер түрінде құрылған, оған декодерленген командалардың орындалуын қамтамасыз ететін микрокомандалар келіп түседі. Буферде бір уақытта 40 микрокоманда бола алады, олар RRF регистрлер блогынан немесе жадыдан таңдалынатын операндтардың дайын болғанына қарай, орындаушы құрылғыларға жіберіледі. Командалар келіп түскен ретпен емес, сәйкес операндтардың және орындаушы құрылғылардың дайын болғанына қарай орындалады. Нәтижесінде кейінірек келіп түскен командалар алдындағы командалардан бұрын орындалуы мүмкін. Сонымен командалардың орындалу реті бұзылады, нәтижесінде параллельлі істеп жатқан орындаушы құрылғылар толығымен жүктеледі де, процессордың өнімділігі артады.

IU1, IU2 (IU - Integer Unit) атқарушы блоктар бүтін сандық операндтарды өңдейді, FPU (Floating - Point Unit) блогы жылжымалы үтірлі сандармен орындалатын операцияларды орындайды, MMX блогы бір уақытта бірнеше упакованные* символдардың өңдеуін қамтамасыз етеді, SSE блогы жылжымалы үтірлі сандардың ағынымен орындалатын операцияларды орындайды.

FPU блогы жылжымалы нүктелі сандармен операцияларды орындайтын командаларды өңдейді. Бұл класқа жылжымалы нүктелі форматта берілген, нақты, бүтін және екілік-ондық сандармен операцияларды орындайтын командалар кіреді. Бұндай көрсетім өңделетін сандардың диапазонын кеңейтуге мүмкіндік береді.

MMX және SSE блоктары SIMD (Single Instruction Multiple Data - Бір Команда - Көп Мәлімет) принципі бойынша мәліметтерді өңдеуге арналған блок алғаш рет Pentium процессорларына енгізілді. Осы принциптің жүзеге асырылуы бір команда көмегімен бір типті ақпараттың бірнеше бірліктері өңдеуге мүмкіндік береді. Мәліметтерді өңдеудің бұл технологиясы MMX (Multi-Media Extension) - “мультимедиалық кеңейту” деп аталады. Себебі ол кескіндер мен дыбыс сигналдардың түрлендіру операцияларының орындау жылдамдығын жоғарлатуға мүмкіндік береді. MMX технологиясын қолдайтын процессорлар упакованные* сандар форматында берілген мәліметтерді өңдейтін кеңейтілген командалар жиынын қамтиды. Pentium III процессорында SIMD принципі бойынша мәліметтерді өңдеу әдісі ары қарай жетілдірілді. Pentium III процессорының кеңейтілген мүмкіндіктері Streaming SIMD Extension (SSE) - “ағындық SIMD - кеңейту” деп аталады. Осы процессорларда жылжымалы нүктелі форматта берілген мәліметтерді SIMD принципі бойынша өңдеуді қамтамасыз ететін SSE технологиясы жүзеге асырылды. Сонымен қатар, Pentium III процессорларына MMX - технологиясының мүмкіндіктерін кеңеәтетін қосымша командалар енгізілген.

MMX командаларды орындаған кезде процессор операндтарды сақтау үшін жылжымалы нүктелі сандарды өңдейтін FPU блогының R7-0 сегіз арифметикалық регистрлерін қолданады. Бұл кезде арифметикалық регистрлер ММ7-0 деп белгіленеді.

Негізгі жадыға жазылатын мәліметті аралық сақтау үшін MOB блогының құрамында жазбаның мәліметтер буфері бар.

Бүркеме-жадыны қолдана отырып, негізгі жадымен алмасу дестелі қатынау циклдары арқылы өтеді. Осы циклдар арқылы бүркеме- жадының бір жолдың құрамын (32 байт) қайта жіберуге болады. Сыртқы 64-разрядты мәліметтер шинасы осындай қайта жіберуді машиналық уақыттың бес тактысында орындауға мүмкіндік береді: бірінші такт жолдың адресін орнатуға арналған, ал келесі төрт такт ішінде мәліметтер беріледі. Бұл кезде алмасуды басқаратын керекті сигналдар бір-ақ рет (циклдың басында) орнатылады, ал беру тактыларындағы адрестің кіші разрядтарының өзгеруі автоматты түрде негізгі жадымен орындалады.

2. 1 КЭШ-жады

Бүркеме жады процессор мен негізгі жады арасында орналасқан, шапшаң әрекетті шектеулі көлемді буферлік жады болып табылады. Жұмыс процесінде информацияның бөлек блоктары негізгі жадыдан бүркеме-жадыға көшіріледі. Негізгі жадыдан бүркеме-жадыға информацияны жуктеу процедурасы бүркемелеу деп аталады. Процессор командаға немесе мәліметтерге қатынағанда алдымен олардың бүркеме-жадыда бар екенін тексереді. Егер керек информация сол жерде болса, онда ол тез алынады, себебі бүркеме-жадыға қатынау процессордың тактілік жиілігімен орындалады. Қатынаудың осы түрін бүркеме-дәл түсу (кэш-попадание) деп аталады. Егер керек информация бүркеме-жадыда болмаса, онда ол негізгі жадыдан алынады және сол сәтте бүркеме-жадыға жазылады. Қатынаудың осы түрін бүркеме-қате түсу (кэш-промах) деп аталады.

Егер бүркеме-дәл түсу бүркеме-қате түсуге қарағанда неғұрлым көп жүзеге асырылса соғұрлым есептеу жүйенің шапшаңдығы өседі.

Р6 процессорларда командаларды және мәліметтерді сақтауға арналған ішкі бүркеме жады қолданылады. Олардың әрқайсысының көлемі 16 Кбайт.

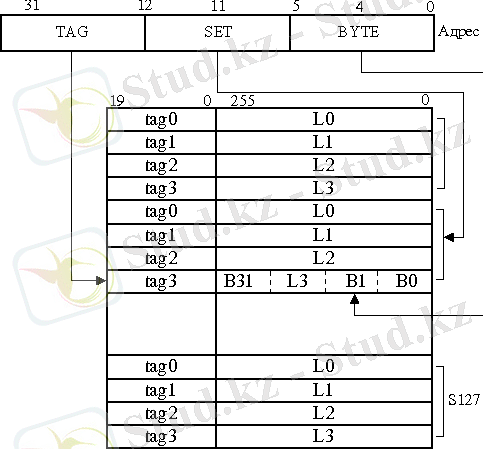

Бүркеме жадының құрылымы 2-ші суретте көрсетілген. Бұл жады ассоциативті типті, ұзындығы 32 байт жолдардан тұрады. Командалар бүрекме-жадыда жолдар 128 жинаққа біріктірілген S0 - S127 және олардың әрқайсысы 4 жолдан (L0, L1, L2, L3) тұрады. Мәліметтердің бүркеме-жадысы екі жолы (L0, L1) бар 256 S0 - S255 жинақтан тұрады.

2 сурет кэш - жадының құрылымы

2. 2 Регистрлер

Регистрлер прграммаларда келесілерді сақтау үшін қолданылады: логикалық және арифметикалық операциялардың операндтарын; адрестің компоненттерін; жады ұяшықтарына нұсқағыштарды. Осы барлық регистрлердің ішінен esp регистрін жеке айтуға болады. Оны программа операндтарын сақтау үшін қолдануға болмайды. Себебі онда программаның стек төбесіне нұсқағыш сақталады. Осы топтың барлық регистрлері өзінің “кіші” бөліктеріне қатынауға мүмкіндік береді. өзіндік адрестеу үшін регитрлердің тек кіші 16- және 8-битті бөліктерін қолдануға болады. Бұл регистрлер арифметикалы-логикалық құрылғының (АЛҚ) ішінде орналасқандықтан, оларды АЛҚ регистрлері деп те атайды:

eax/ax/ah/al (Accumulator register) - аккумулятор. ebx/bx/bh/bl (Base register) - базалық регистр. Жадыда кейбір объектінің базалық адресін сақтауға арналған.

ecx/cx/ch/cl (Count register) - регистр-санағыш.

edx/dx/dh/dl (Data register) - мәліметтер регистрі.

Бұл екі регистр тізбекті операцияларды қолдау үшін қолданылады

esi/si (Source Index register) - түптектің индексі. edi/di (Destination Index register) - қабылдауыш индексі.

Стекпен жұмыс жасау үшін шағынпроцессордың командалар жүйесінде арнайы командалар бар, ал шағынпроцессордың программалық моделінде бұл үшін арнайы регистрлер бар.

esp/sp (Stack Pointer register) - стек нұсқағышының регистрі. ebp/bp (Base Pointer register) - стектің кадр базасының нұсқағыш регистрі.

3. IDIV командасы

Таңбасы бар сандарды бөлу үшiн IDIV командасы арналған. Таңбасы бар сандар мен командаларға қатысты қарастырылған барлық жағдайлар бұл команда үшiн әдiл тек қана санның таңбасы болған жайда нолге бөлу ерекшелiгiн атап өтейiк ол IDIV командасын орындаған кезде келесi себебтерден туындайды:

- бөлгiш нөлге тең болса.

- ол үшiн арнай бөлiнген разрятық торға жеке кiрмейдi .

BSR операнд1. операнд2(bit scaning reset) - биттi сканерлеу бұл команда биттердi жоғарыдан төмен қарай iздейдi. Егер мұндай табылса операнд1 осы биттiң нөмiрi ьүiн санды мiн тұрiнде енгiзiледi. Бұл кезде бiрiншi бiрлiк битiң позицисы нол биттке салыстырмалы түрде есептеледi. Егер операнд2 битттерi нөлге тең болса онда ZF жалаушасы бiрге орнатылады, керi жағдайда ZF нөлге айналады.

4. Қорытынды

Бұл курстық жобада микропроцессордың структурасы зерттелді. Анығырақ процессорының жұмысы қарастырылды. Процессорлар Intel - ң шағынпроцессорлардың жолын жалғастырып, Intel фирмасының модельдерінің алдыңғы шағынпроцессорларға қарағанда бірқатар архитектуралық және құрылымдық ерекшеліктерге ие. Бұл курстық жобада қолданылған алгоритм программалау тілінде жазылған программа арқылы тексерілді.

Осы жобаны жасай отырып процессорлар әлемiндегi дүниетанымым кеңейе түстi.

Пайдаланылған әдебиеттер тiзiмi

- И. И. Шагурин “Процессоры семейства Р6”. Санкт-Петербург “Питер”, 2002.

- В. Юров “ASSEMBLER”. Санкт-Петербург “Питер”, 2001.

3. Internet желiсi

А ҚосымшаСЫ

BSR командасының орындалуы

В Қосымшасы

IDIV командасының орындалуы

С Қосымшасы

Программаның листингі

unit U1;

interface

uses

Windows, Messages, SysUtils, Classes, Graphics, Controls, Forms, Dialogs,

Menus, ExtCtrls, StdCtrls, ComCtrls, MMSystem, Buttons;

type

TForm1 = class(TForm)

Image1: TImage;

Shape1: TShape;

Shape2: TShape;

Shape3: TShape;

Shape4: TShape;

Shape5: TShape;

Shape6: TShape;

Shape7: TShape;

Shape8: TShape;

Shape9: TShape;

Shape10: TShape;

Shape11: TShape;

Shape12: TShape;

Shape13: TShape;

Shape14: TShape;

Shape15: TShape;

Shape16: TShape;

Shape17: TShape;

Shape18: TShape;

Shape19: TShape;

Shape20: TShape;

Label1: TLabel;

Label2: TLabel;

Label3: TLabel;

Label4: TLabel;

Label5: TLabel;

Label6: TLabel;

Label7: TLabel;

Label8: TLabel;

Label9: TLabel;

Label10: TLabel;

Label11: TLabel;

Label12: TLabel;

Label13: TLabel;

Label14: TLabel;

Shape21: TShape;

Label15: TLabel;

Label16: TLabel;

Label17: TLabel;

Label18: TLabel;

Label19: TLabel;

Label20: TLabel;

BitBtn1: TBitBtn;

Button1: TButton;

Button2: TButton;

Button3: TButton;

Button4: TButton;

Button5: TButton;

Button6: TButton;

Button7: TButton;

Button8: TButton;

Shape22: TShape;

Label30: TLabel;

Label31: TLabel;

Label32: TLabel;

Button10: TButton;

Button11: TButton;

Label33: TLabel;

Button12: TButton;

Button13: TButton;

Button14: TButton;

Button15: TButton;

Button16: TButton;

Button17: TButton;

Button18: TButton;

Label34: TLabel;

Label35: TLabel;

Label36: TLabel;

Shape23: TShape;

procedure Button1Click(Sender: TObject) ;

procedure Button2Click(Sender: TObject) ;

procedure Button3Click(Sender: TObject) ;

procedure Button4Click(Sender: TObject) ;

procedure Button5Click(Sender: TObject) ;

procedure Button6Click(Sender: TObject) ;

procedure Button7Click(Sender: TObject) ;

procedure Button8Click(Sender: TObject) ;

procedure Button9Click(Sender: TObject) ;

procedure Button11Click(Sender: TObject) ;

procedure Button13Click(Sender: TObject) ;

procedure Button18Click(Sender: TObject) ;

private

{ Private declarations }

public

{ Public declarations }

end;

var

Form1: TForm1;

implementation

uses u3;

{$R *. dfm}

procedure TForm1. Button1Click(Sender: TObject) ;

begin

shape18. Visible:=true;

shape1. Visible:=true;

Label1. Visible:=true;

Label2. Visible:=true;

Button1. Visible:=false;

Button10. Visible:=false;

end;

procedure TForm1. Button2Click(Sender: TObject) ;

begin

shape2. Visible:=true;

Label3. Visible:=true;

Label4. Visible:=true;

Button2. Visible:=false;

Button12. Visible:=false;

end;

procedure TForm1. Button3Click(Sender: TObject) ;

begin

shape3. Visible:=true;

shape4. Visible:=true;

Label5. Visible:=true;

Label6. Visible:=true;

Label7. Visible:=true;

Label8. Visible:=true;

Label9. Visible:=true;

Label10. Visible:=true;

Button3. Visible:=false;

Button13. Visible:=false;

end;

procedure TForm1. Button4Click(Sender: TObject) ;

begin

shape5. Visible:=true;

Label11. Visible:=true;

Label12. Visible:=true;

Label13. Visible:=true;

Button4. Visible:=false;

Button14. Visible:=false;

... жалғасы- Іс жүргізу

- Автоматтандыру, Техника

- Алғашқы әскери дайындық

- Астрономия

- Ауыл шаруашылығы

- Банк ісі

- Бизнесті бағалау

- Биология

- Бухгалтерлік іс

- Валеология

- Ветеринария

- География

- Геология, Геофизика, Геодезия

- Дін

- Ет, сүт, шарап өнімдері

- Жалпы тарих

- Жер кадастрі, Жылжымайтын мүлік

- Журналистика

- Информатика

- Кеден ісі

- Маркетинг

- Математика, Геометрия

- Медицина

- Мемлекеттік басқару

- Менеджмент

- Мұнай, Газ

- Мұрағат ісі

- Мәдениеттану

- ОБЖ (Основы безопасности жизнедеятельности)

- Педагогика

- Полиграфия

- Психология

- Салық

- Саясаттану

- Сақтандыру

- Сертификаттау, стандарттау

- Социология, Демография

- Спорт

- Статистика

- Тілтану, Филология

- Тарихи тұлғалар

- Тау-кен ісі

- Транспорт

- Туризм

- Физика

- Философия

- Халықаралық қатынастар

- Химия

- Экология, Қоршаған ортаны қорғау

- Экономика

- Экономикалық география

- Электротехника

- Қазақстан тарихы

- Қаржы

- Құрылыс

- Құқық, Криминалистика

- Әдебиет

- Өнер, музыка

- Өнеркәсіп, Өндіріс

Қазақ тілінде жазылған рефераттар, курстық жұмыстар, дипломдық жұмыстар бойынша біздің қор #1 болып табылады.

Ақпарат

Қосымша

Email: info@stud.kz