16-разрядты микропроцессор негізіндегі деректерді жинақтау құрылғысын жобалау: ОЕСҚ ұйымдастыру, ассемблерлік бағдарламалау және тезәрекеттілікті бағалау

ЕСЕПТІК-ГРАФИКАЛЫҚ ЖҰМЫСҚА ТАПСЫРМА:

Келесі түрде жұмыс істейтін деректерді жинақтау құрылғысын (ДЖҚ) жобалау керек: (АК) арналар коммутаторының F кірістеріне келіп түсетін аналогты сигналдарды тізбек бойынша сұрап шығып, аналогты-цифрлық түрлендіргіш (АЦТ) көмегімен цифрлық сигналға түрлендіріп, (1 байт=8бит разрядты екілік сөз) оларды оперативті есте сақтау құрылғысының (ОЕСҚ) М символдық аты бар адресті ұяшықтан басталатын аймағына орналастыру керек.

ДЖҚ-ның құрамында адрестік сөзінің форматы 2 байт =16 бит және Q = N·n сыйымдылықты ОЕСҚ-сы бар. Микропроцессорлық жүйенің жұмысын синхрондау тактілік импульстер генераторының (ТИГ) көмегімен іске асады. Синхрондау жиілігі f=500 кГц.

Талап етіледі:

а) ОЕСҚ ұйымдастыруды қарастыру;

б) 16-разрядты микропроцессор (МП) негізінде орындалған микропроцессорлық құрылғы түріндегі ДЖҚ-ны іске асыру. Бұл кезде кезекті арналардың адресі 1 кестесіне сәйкес берілген нұсқа бойынша R регистрінде сақталу керек. Микропроцессорлық құрылғыны құрылымдық схема түріне келтіріп жұмыс істеуінің программасын ассемблер тілінде құру керек және программаның жадысында BEG адресті ұяшығынан бастап орналасу кестесін келтіріп, программаны кодалық комбинацияларда (машиналық тілде) жазу;

в) ДЖҚ-ның тезәрекеттілігін анықтау.

МАЗМҰНЫ:

Кіріспе . . . 4

Есептік-графикалық жұмысқа тапсырма . . . 5

1. 1 Оперативті есте сақтау құрылғысын (ОЕСҚ) ұйымдастыру . . . 6

1. 2 Мәліметтерді жинақтау циклының соңын білдіретін белгіні қалыптастыру . . . 8

Ассемблер тілі туралы қысқаша мәлімет . . . 10

1. 3 Микропроцессорлық құрылғының тезәрекеттілігін бағалау . . . 11 Пайдаланылған әдебиеттер тізімі . . . 14

Кіріспе

ЕСЕПТІК-ГРАФИКАЛЫҚ ЖҰМЫСТЫҢ мақсаты: «Интегралдық және микропроцессорлық схемотехника» курсын оқып үйренуде алған білімдерін бекіту. Микропроцессорлық құрылғы түрінде деректерді жинау құрылғысын ұйымдастыру тәсілдеріне арналған. Мұнда күрделі микропроцессорлық техниканы оқып үйренудің бастапқы этапында деректер жинаудың есептеу процессін ұйымдастыру үшін Intel 8080 (аналогтары KP580ИК80 және КР580ВМ80А) немесе i8085 (аналогы K1821BM85A) сегізразрядты қарапайым модельдерін қолдану керек.

Байланыс арналарын өлшеу немесе телеметриялық ақпаратты электронды-есептеу машинасына (ЭЕМ) қабылдау кезінде мәліметтер жинауды қамтамасыз ету қажеттілігі жиі туады. Ол кезде ток немесе кернеу түріндегі аналогтық сигналдарға сұраныс жасау, оларды цифрлық түрге түрлендіріп, одан ары қарай өңдеп және көрсету мақсатымен оперативті жадының (ОЕСҚ) белгілі бір аймағына орналастырумен бірге орындалады.

ЕСЕПТІК-ГРАФИКАЛЫҚ ЖҰМЫСҚА ТАПСЫРМА

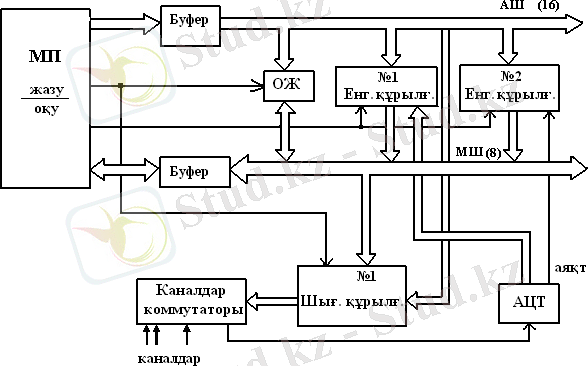

Микропроцессорлық құрылғы (МПҚ) түрінде құрастырылған ДЖҚ-ның құрылымдық схемасы 2 суретінде көрсетілген. МПҚ құрамында микропроцессор, АЦТ, оперативті жады (ОЖ) аналогты арналар коммутаторынан басқа екі енгізу және бір шығару құрылғылары бар, олардың жұмысын программалы-басқармалы регистр-порттар атқарады. Мысалы, К589ИР12 көпрежімді буферлік регистрлер (КБР) . Бұл вариант бойынша МПҚ мен басқару шинасы екі жолақтан ғана тұра алады: ЖАЗУ және ОҚУ.

Суретте:

МП - Микропроцессор

АЦТ - аналогты-цифрлық түрлендіргіш

АШ - адрестер шинасы

МШ - мәліметтер шинасы

ОЖ - операциялық жүйе

ДЖҚ- Деректер жинау құрылғысы

2 сурет . Микропроцессорлық құрылғы (МПҚ) түрінде құрастырылған Деректер жинау құрылғысының (ДЖҚ) құрылымдық схемасы .

- Оперативті есте сақтау құрылғысын (ОЕСҚ) ұйымдастыру

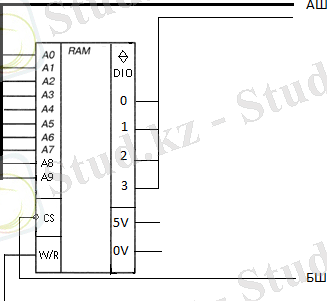

Оперативті жады жартылайөткізгішті ОЕСҚ-ның үлкен интегралды схемаларында (ҮИС) ұйымдастырылған.

59-НҰСҚА

N соң. алд =5

F 10 =12=С

R=С

N соңғы =9

M=03E5

Q=1024x8

BEG=071F

Берілгені:

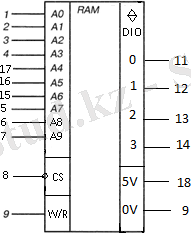

Микросхема типі: КP541РУ5

Сыйымдылығы:1К x8

Цикл уақыты: (55) (таңдау), нс

Қоректену қуаты, мВт: <500

Қоректену кернеуі, В: 5

Технология: ИИЛ-ТТЛ

KР541PУ5 -Оперативті есте сақтау құрылғысы сыйымдылығы 4078-ға тең массасы 4г кем емес адрестік және разрядтық басқарылуы бар микросхема.

Оперативті жадының m микросхемалар санын анықтаймыз:

; ( k=1024)

бұл жерде М 1 - таңдалған микросхемалардың бірінің сыйымдылығы.

Әр жолақтағы микросхемалар саны :

;

бұл жерде n тал - талап етілген разрядтылық;

n таң - таңдап алынған микросхема разрядтылығы.

m жол жолақтар санын келесі формуламен анықтаймыз:

;

ОЕСҚ микросхемаларына екілік сөздерді жазу мен одан оқу режімдерін қамтамасыз ету үшін RD/WR (оқу/жазу) кірістері қарастырылған. RD/WR = 0 кезінде жазу режімі, ал RD/WR = 1 болғандағы оқу режімін қолданамыз.

1. 1. 2 8-разрядты микропроцессор базасында микропроцессорлық құрылғы түрінде ДЖҚ-ны іске асыру.

1. 2 Мәліметтерді жинақтау циклының соңын білдіретін белгіні қалыптастыру.

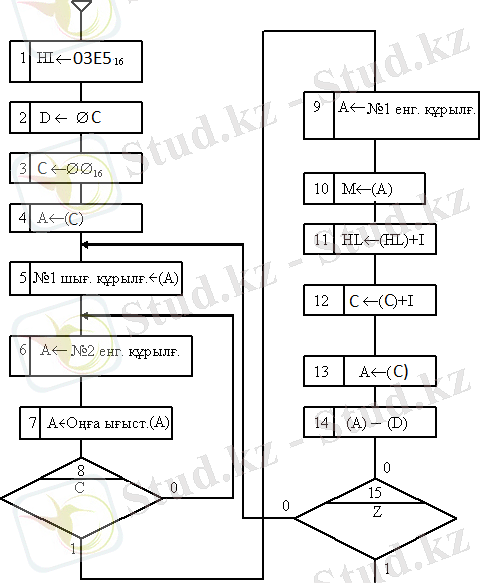

Мәліметтер жинау алгоритмінің блок-схемасын құрастыру.

Мәліметтер жинау алгоритмінің блок-схемасы

Блок-схемаға қысқа түсініктеме берейік. I блокта HL регистрлер жұбына M=003С бастапқы адресі енгізіледі. II блокта D регистріне 8 10 (10h ) санын енгізу керек. III блокта R =B регистрі аналогты каналдар санының санағышы қызметін атқарады. Оған алғашқы каналдың адресі ØØh енгізіледі. Келесі кезекте бұл адрес аккумулятор және №1 шығару құрылғысы арқылы (4 пен 5 блоктары) коммутатордың адрестік кірісіне келіп түседі. Коммутатор адресі көрсетілген арнаны АЦТ кірісіне қосады да түрлендіруді орындайды. АЦТ түрлендіру жұмысын аяқтағанша МПҚ күту режіміне көшеді (6, 7 және 8 блоктары) . АЦТ-ның аяқт. шығысынан сигнал №2 енгізу регистр-портының кіші разрядына келеді. Аяқт. =0 болса АЦТ жұмысы аяқталмағанын білдіреді. Бұл кезде 6-8 блоктары нөл триггер-жалауының жұмысын қамтамасыз етеді және программа кіші цикл бойынша орындалады. Бағдарламаның осылай орындалу режімі АЦТ-ның аяқт. шығысындағы сигнал 1 болғанға дейін қайталанады. Бұл күту режімін қамтамасыз етеді. Аяқт. =1 болғанда ғана 8 блогының командасы орындалып АЦТ шығысындағы түрленген сигнал С=1болады, яғни аналогты сигнал цифрлыға түрленеді және № 1 енгізу құрылғысы арқылы микропрцессордың аккумуляторына келіп одан берілген оперативті жады ұяшығына жазылады (9 және 10 блоктары) . 11 және 12 блоктарында кезекті аналогты арна мен келесі ақпаратты жазуға жады ұяшығының адрестері қалыптасады. Арнаның жаңа адресі аккумуляторға жіберіледі (13 блогы) . 14 блогында В және D регистрлеріндегі деректер салыстырылады. B =D = 0 теңдігі барлық арналардағы ақпарат оқылып, z = 1 нөлдік белгісі шыққанын, яғни деректерді жинақтау аяқталғанын көрсетеді. Егер z = 0 болса, яғни салыстыру операциясынан кейін аккумулятордағы мәлімет өзгермесе адресі 13 блогында енгізілген келесі арнадан ақпарат оқылады. 12 блогында көрсетілген E регистріндегі кезекті аналогты арнаның адресі I∅ 16 санына тең болғанша программа үлкен цикл бойынша қайталанады.

Нұсқа бойынша жасалынған Ассемблер тіліндегі программасы.

Командалар №

Команды

Ескерту :оңға ығыст. (А) - А регистріндегі (аккумулятор) деректі оңға ығыстыру, ШӨ - шартты өту.

Ассемблер тілі туралы қысқаша мәлімет .

Ассемблер тілі - машиналық тідің аналогы болып саналады. Ассемблер тілінде жазылған программа МП-р құрылысының ерекшеліктерін: жадтың ұйымдастырылуын, операндтарды адрестеу тәсілдерін, регистрлерді қолдану ережелерін анықтап, көрсету қажет. Әр МП-ң өзінің Ассемблері болады.

Ассемблер тілінде жазылған программа жад сегменттері деп аталатын жадблоктарының тобынан тұрады. Программа осындай бір немесе бірнеше блок-сегменттерден тұруы мүмкін. Әр сегмент программа кодының әр қатарында орналасқан сөйлемдерден құрылады.

Ассемблер тілінің сөйлемдері төрт түрлі болады:

- Командалар: машиналық кодтардың аналогтары. Бұл командалар трансляциялау кезінде МП-ң сәйкес командаларына түрленеді;

- Макрокомандалар: трансляциялау кезінде басқа сөйлемдерге алмасатын сөйлемдер;

- Дерективалар: ассемблер трансляторына орындалатын әрекеттер туралы түсінік береді, яғни қызметші ақпараттар жиыны. Дерективалар машиналвқ кодтарға түрленбейді;

- Комментарий: кез-келген белгілерден тұрады.

Ассемблер тілінің екі артықшылығы бар:

Бұл тілдің көмегімен программаны МП командалары деңгейінде жазуға болады және сандық кодтардың барлығын еске сақтауды талап етпейді. Программа командалары жазылып болған соң, Ассемблер программасы шақырылады да, ол бұл командаларды олардың кодтарына айналдырады. Командалар жиыныннан тұратын программа негізгі не алғашқы программа деп аталады, ал негізгі программаның сандық кодтары, яғни машиналық тілге айналған түрі - объектік программа деп аталады.

Ассемблердің атқаратын негізгі қызметі - қолданушыға түсінікті негізгі прогрпмманы МП түсінетін объекттік программаға айналдыру. Ассемблердің кең тараған түрлері: IBM фирмасының MASM(Macro Assembler) программасы және Borland фирмасының TASM (Turbo Assembler) прграммасы.

Программаның жадыда орналасуы

071F

0720

0721

0722

0723

0724

0725

0727

0728

0729

072A

072C

072D

072E

072F

0730

0736

0737

0738

Командаға керек ОЖ ұяшықтар саны команданың байттар санымен анықталады.

Программа кодалық комбинация түрінде көрсетілуі.

... жалғасы- Іс жүргізу

- Автоматтандыру, Техника

- Алғашқы әскери дайындық

- Астрономия

- Ауыл шаруашылығы

- Банк ісі

- Бизнесті бағалау

- Биология

- Бухгалтерлік іс

- Валеология

- Ветеринария

- География

- Геология, Геофизика, Геодезия

- Дін

- Ет, сүт, шарап өнімдері

- Жалпы тарих

- Жер кадастрі, Жылжымайтын мүлік

- Журналистика

- Информатика

- Кеден ісі

- Маркетинг

- Математика, Геометрия

- Медицина

- Мемлекеттік басқару

- Менеджмент

- Мұнай, Газ

- Мұрағат ісі

- Мәдениеттану

- ОБЖ (Основы безопасности жизнедеятельности)

- Педагогика

- Полиграфия

- Психология

- Салық

- Саясаттану

- Сақтандыру

- Сертификаттау, стандарттау

- Социология, Демография

- Спорт

- Статистика

- Тілтану, Филология

- Тарихи тұлғалар

- Тау-кен ісі

- Транспорт

- Туризм

- Физика

- Философия

- Халықаралық қатынастар

- Химия

- Экология, Қоршаған ортаны қорғау

- Экономика

- Экономикалық география

- Электротехника

- Қазақстан тарихы

- Қаржы

- Құрылыс

- Құқық, Криминалистика

- Әдебиет

- Өнер, музыка

- Өнеркәсіп, Өндіріс

Қазақ тілінде жазылған рефераттар, курстық жұмыстар, дипломдық жұмыстар бойынша біздің қор #1 болып табылады.

Ақпарат

Қосымша

Email: info@stud.kz