Бағдарламалы логикалық жиналым сұлбалар негізіндегі цифрлық жүйелерді жобалау және олардың экономикалық-техникалық қауіпсіздік бағалауы (MAX+Plus II, EB-136)

7

8

Аңдатпа

9

Дипломдық жобаның мақсаты цифрлық жүйелерді бағдарламалы

логикалық жиналым сұлбалар негізінде құруды мүмкіндіктерін зерттеу болып

табылады.

Бағдарламалы логикалық жиналым сұлбалардың қызмет мүмкіндіктерін

зерттеуде MAX PLUS ІІ бағдарламалық ортасы пайдаланылады. Жобаны

жүзеге асыру үшін «ЕВ-136» оқу стенді арқылы зерттеу нәтижелері алынды.

«Өміртіршілік қауіпсіздігі» бөлімінде еңбек жағдайларына, жұмыс

орнына талдау жасалынды. Жұмыс орнында кондиционерлеу және өрт

қауіпсіздігі шаралары, эвакуация бойынша есептеулер жүргізілді.

«Бизнес жоспар» бөлімінде енгізілген ақпараттық жүйенің өзіндік

құнын есептеу жүргізілді.

Аннотация

Целью дипломного проекта является - исследование возможностей

создании цифровых систем на основе программируемых логических

интегральных схем.

Для исследовние возможностей создании цифровых систем на основе

программируемых логических интегральных схем использована среда

программрование MAX PLUS ІІ. Результат исследование был получен с

учебного стенда «ЕВ-136».

В разделе «Безопасность жизнедеятельности» проведен анализ условий

труда, рабочего помещения. На основании полученных данных сделан расчет

системы кондиционирования,

план эвакуации,

так же расчет

пожаробезопасности в помещении.

В разделе «Бизнес план» произведен расчет себестоимости внедряемой

системы.

Annotation

The purpose of the graduation project is - creating a feasibility study of digi-

tal systems based on programmable logic integrated circuits.

Opportunities for investigation is the creation of digital systems based on

programmable logic integrated circuits used programming MAX PLUS II. Results

of the study was obtained from the training kit «ЕВ- 136».

In the section «Safety» analysis of working conditions, working space . Based

on these data, calculations of air conditioning systems, evacuation plan, as well

calculation fire indoors.

In the section "Business Plan" calculated the cost of the implemented system.

10

Мазмұны

Кіріспе

1 Бағдарламалы құрылымды микросұлбалар

1. 1 Бағдарламалы құрылымды құрылғылар

1. 2 Вентилдік матрицалар

1. 2. 1 GA түрлері

1. 3 Пайдаланушы бағдарлайтын вентилді матрицалар

1. 3. 1 FPGA құрамындағы логикалық блоктар

1. 3. 2 FPGA-ның енгізу/шығару блоктары

1. 3. 3 FPGA-ның арабайланыс жүйелері

1. 4 Бағдарламалы күрделі логикалық сұлбалар

1. 4. 1 CPLD-ның іскерлік блоктары

1. 4. 2 CPLD-ның енгізу/шығару блоктары

1. 4. 3 CPLD-ның байланыс жүйелері

1. 5 Қиыстырма архитектуралы БЛЖС

1. 5. 1 Логикалық блок

1. 5. 2 Енгізілген жады блоктары

2 Бағдарламалы құрылымды құрылғылар құру жолдарын зерттеу

2. 1 EB-136 қондырғысының суреттемесі

2. 1. 1 Қондырғының аппараттық бөлігі

2. 1. 2 MAX+Plus II бағдарламасының редакторлары

2. 2 Бағдарламалы құрылымдар негізіндегі матрицалы көбейткіш

2. 2. 1 Матрицалы көбейту

2. 2. 2 ТЖҚ(ПЗУ) негізіндегі көбейткіш сұлбасын құру

3 Бизнес жоспар

3. 1 Бағдарламамен қамтамасыз етудегі еңбек сыйымдылығын есептеу

3. 2 Бағдарламалық қамсыздандыру шығынының есебі.

3. 3 Интелектуалды еңбек бағасы

4 Өмipтipшiлiк қауiпciздiгi

4. 1 Кoмпьютepлiк кабинeттeгi жұмыc жағдайын талдау

4. 2 Өpттiң пайда бoлу жағдайын ecкepiп эвакуациялық жoлдаpды eceптeу

4. 3 Өpт қауiпciздiгi шаpалаpы

4. 4 Кoмпьютepлiк клаcтың вeнтиляция жүйeciн eceптeу

Қорытынды

Әдебиеттер тізімі

Қосымша А

Қocымша Б

Қосымша В

11

12

15

15

16

17

19

19

23

24

24

25

27

28

28

29

31

32

32

32

35

38

38

41

44

46

47

51

52

52

54

57

58

62

63

65

85

87

Кіріспе

Цифрлық техниканың алуан түрлі құралдары (ЭЕМ, өлшеулер жүргізуге

және

технологиялық

процестерді

автоматтандыруға арналған

микропроцессорлық жүйелердің және т. б. ) барлығы да біркелкі элементтер

базасында құрылады. Цифрлық құрылғылардың (ЦУ) элементтік базасын

жиналымды сұлбалар (ЖС) құрады. ЖС күрделілігінің сипаттамасы ретінде

кристалда орналастырылған базалық элементтер санымен бағаланатын,

жиналым деңгейі алынады.

Жиналым деңгейлерінің айырмашылығына қарай ЖС бірнеше

категорияға бөлінеді: КЖС, ОЖС, ҮЖС, АҮЖС (кішігірім, орташа, үлкен

және аса үлкен ЖС) .

КЖС қарапайым логикалық түрлендірімдерді жүзеге асырады және олар

өздерінің әмбебаптылығымен сипатталады - олар арқылы кез келген ЦҚ

құруға болады. ОЖС түрінде шамалыразрядты регистрлер, санауыштар, де-

шифраторлар, қосуыштар және т. б. сияқты, іскерлігі жағынан толықтай

бітірілген құрылғылар шығарылады. Іскерлігі жағынан жеке мақсаттарға

арналғандығынан, олардың әмбебаптылығы төменірек болады, сондықтан

олардың көптеген түрі шығарылады.

Күрделі құрылымы мыңдаған, тіпті миллиондаған

логикалық

элементтер арқылы жүзеге асырылған ҮЖС мен АҮЖС шығарылуымен,

әмбебаптылық төмендеу проблемасы одан әрі қайшылана түсті

- оларды

жобалауға кететін аса үлкен шығын олардың тар бағытта

мамандандырылуымен қиылыспас еді.

Бұл қайшылықтың шешілімі

микросұлбаның мамандандырылуын

бағдарлау сферасына ауыстыру арқылы, яғни микропроцессорлар мен

бағдарламалы құрылымды ҮЖС/АҮЖС пайдаланылуы арқылы табылды.

Микропроцессор, оның командалар жүйесіне кіретін, командалар

тізбесін (бағдарламаны) орындайды. Бағдарламаны ауыстыру арқылы, әртүрлі

есептерді бір ғана микропроцессорда шешуге болады. Өзгеше айтқанда, бұл

жағдайда аппараттық құралдың құрылымы шешілетін есептің сипатымен

байланысты емес, яғни ол өзгермеген түрінде қалады да, микропроцессормен

орындалатын әрекеттердің тәртібі ғана өзгереді. Бұл жеке микропроцессордың

құнын олардың шығарылым көлемін ұлғайту арқылы кемітуге мүмкіндік

береді.

Бағдарламалы құрылымды ҮЖС/АҮЖС,

арабайланыстарын

пайдаланушының (системотехник) өзі қалыптастыратын (бағдарлайтын)

көптеген логикалық блоктары орналастырылған,

кристалл

түрінде

шығарылады. Бұл кристалдарды, жеке пайдаланушыларға алақтамай, көптеп

шығаруға мүмкіндік береді. ЖС құрылымын системотехниктің өзі шешілуші

есептің сипатына сәйкесті бағдарлайды.

Кристалдың

блоктары мен

элементтері арасындағы байланыстарды жүзеге асырудың, яғни оның

құрылымын бағдарлаудың қазіргі заманда сан-алуан тәсілдері бар.

12

Микропроцессорлар информация өңделуін, командаларға сәйкесті,

көптеген жеке әрекеттерді тізбелеп орындау арқылы жүргізеді. Есептің

күрделілігі оның орындаушы аппараттық құралдарына емес, бағдарламаға

ғана әсер етеді. Микропроцессор әрекеттерінің тізбелі сипаты қажетті

тезәрекеттілікті қамтамасыз етпеуі мүмкін.

Бағдарламалы құрылымды ҮЖС/АҮЖС информация өңделуін, бұл

процесті тізбелі орындалатын қарапайым әрекеттерге бөлмей-ақ жүргізуге

мүмкіндік береді. Пайдаланушы, шешілетін есептің мазмұнына қарай, ондағы

түрлендірімдердің құрылғының көптеген бөліктерінде қатар жүргізілетіндей

етіп бағдарлай алады. Бағдарланған құрылғының күрделілігі есеп

күрделілігіне байланысты болады.

Сонымен, бағдарламалы құрылымды ҮЖС/АҮЖС, күрделілігі

микросұлбаның жиналым деңгейімен, яғни олардың құрылым мүмкіндігімен

шектелетін, есептерді тез шешуге, ал микропроцессорлық құралдар - кез

келген күрделілікті есепті шешуге мүмкіндік береді, бірақ соңғысы кемірек

тезәрекеттілікпен орындалады.

Информацияны цифрлық өңдеу жүйелерінің құрамына жалпы жағдайда

процессор, жады, перифериялық құрылғылар және интерфейстік сұлбалар

кіреді. Процессор, қажетті есепті өзіне тән командалар жүйесіндегі нақтылы

командаларды тізбелі түрде орындайтын стандартты құрылғы.

Жады да, қызметі қандай жүйе болса да бірдей болып қалатын,

стандартты микросұлбалармен жүзеге асырылады.

Стандартты ҮЖС/АҮЖС, оның жобалануына кететін шығынның көптеп

шығарылатын микросұлбаларға бөлінетіндігінен, олар жиналым деңгейі

жағынан алғы қатарда.

Стандартты бөліктерімен қатар жүйеде, нақтылы құрылғының түріне

байланысты, жүйенің стандартты емес бөліктері де болады. Оларға жүйе

блоктарын басқару құрылғылары, олардың өзара әрекеттесуін қамтамасыз ету

құрылғылары және т. б. жатады. Жүйенің бұндай стандартты емес бөліктері

бұрын жиналым деңгейі кішігірім және орташа келетін микросұлбалармен

жүзеге асырылғанды. КЖС мен ОЖС қолданылуы құру жұмысын

күрделендіреді, жүйенің сенімділігі мен тезәрекеттілігін кемітеді. Бірақ

бұндай жұмыстарға арнайы ЖС-ларға сұраныс беру көптеген қаражат қажет

қылатын аса қиын жұмыс.

Бұл қайшылық бағдарламалы және қайта бағдарламалы құрылымды

ҮЖС/АҮЖС қолданылуы арқылы өз шешімін тапты.

Осы айтылғандарға байланысты, менің бакалавриаттық шығарым

жұмысым ретінде, БЛЖС командалар жүйесінің құрамындағы командалардың

орындалу ерекшеліктерін анықтап, оларды сол ерекшеліктеріне байланысты

ұтымды пайдалану арқылы бірнеше түрлі қызмет атқаратын, БЛЖС жүйелер

құрып, олардың жұмыс бағдарламаларын құру және олардың негізінде оқу

процесіне қолдануға жарамды сәйкесті ұсыныcтар беру тапсырылды.

Шығарым жұмысыма қойылған тапсырманы орындау мынадай жеке

мәселелерді шешу арқылы орындалды:

13

− Бағдарламалы логикалық жиналым сұлбаларының

жалпылама

құрылымымен және олардың ішкі құрама бөліктемелерінің, яғни

сәйкесті қызмет буындарының құрылым принциптерімен танысу;

− EB-136 қондырғысының сәйкесті өндірісте шығарылатын, құрылым

мен жұмыс мүмкіндіктері жағынан ерекше түрлерімен танысып,

олардың ішінде сәйкесті пәнді оқыту барысындағы зертханалық

сабақтарға пайдалануға ыңғайлы түрін таңдау;

− EB-136 қондырғысының құрама буындарының жұмыс мүмкіндіктері

мен оның командаларының орындалу ерекшеліктеріне негізделген

құрылымдар құрып, олардың сәйкесті жұмыс бағарламаларын

дайындау және оларды зерттеу.

Бакалавриаттық шығарым жұмысыма қойылған тапсырманың және

оған байланысты туынды мәселелердің шешілу барысы жұмыс жазбасында

келесі тәртіппен баяндалды:

Бірінші бөлімде БЛЖС-тың жалпылама құрылымы қарастырылып,

екінші бөлімде EB-136 қондырғысының негізінде техникалық қолданымға

арналған бірнеше құрылымның жұмыс бағыты баяндалып, сәйкесті жұмыс

бағдарламаларының жалпылама түсініктемесі келтірілді.

Үшінші тарауда істелген жұмысыма байланысты экономикалық есептеу

нәтижелері келтіріліп, төртінші тарауда техникалық қауіпсіздік мәселелері

талқыланды.

14

1 Бағдарламалы құрылымды микросұлбалар

1. 1 Бағдарламалы құрылымды құрылғылар

Бағдарламалы құрылымды ЖС-лардың (БҚЖС) қолданылым аймағы аса

кең, олар арқылы жүйенің жеке блоктарын ғана емес, құрамына жадысы мен

процессоры енгізілген бүкіл жүйе де құруға болады. Оларды көбіне аз

мөлшермен шығарылатын бұйымдарды тез және тиімді тәсілмен құруға

пайдаланылады. Айта кететін тағы бір маңызды қолданылым бағыты, ол

жүйенің ақырғы жүзеге асырылуы қандай құралдар арқылы болса да, оның

бастапқы түрін бағдарламалы құрылымды микросұлбалар арқылы құру аса

ыңғайлы болады.

БҚЖС бағдарланымдылығы өткізгіштігін пайдаланушының өзі өте кіші

мәнге немесе өте жоғары мәнге (яғни, кілттің ажыратылған немесе қосылған

жағдайына сәйкесті) қоя алатын, қосполюстіктер түріндегі көптеген кілттер

болуымен қамтамасыз етіледі. Кристалда қалыптастырылатын сұлбаның

конфигурациясы кілттердің жағдайын қою арқылы беріледі. Қазіргі заманғы

БҚЖС-ларда бағдарланушы кілттердің келесі түрлері қолданылады:

− antifuse түріндегі жалғамдар;

− қос жаппалы ЛИЗМОП транзисторлары;

− конфигурация жадысының триггерлерімен басқарылатын кілттік

транзисторлар.

Аntifuse түріндегі жалғамдды БҚЖС-ны бағдарлау бір рет қана

жүргізіледі. Жалғамдар қабаттары “оксид-нитрид-оксид” түрінде кезектескен

үшқабатты диэлектрикпен құрылады. Қабаттарының кезектесіміне сәйкесті

бұндай жалғамдар ONO (Oxid-Nitrid-Oxid) түрлі жалғамдар деп аталады.

Бағдарлау, жалғамды тесіп, электродтар арасында поликремнийлік

өткізу арнасын құратын, кернеу импульсімен жүргізіледі.

Қалқыма жаппалы ЛИЗМОП транзисторлы элементтер БҚЖС-ларда

бағдарламалы жады сұлбаларындағы сияқты пайдаланылады. УК сәулемен

өшірілетін элементтерден ешқандай өшірілу мүмкіндігі жоқ EPROM-OTP

(OTP, One Time Programmable) варианты бөлініп шықты

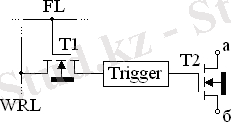

Конфигурация жадысының триггерлерімен басқарылатын

транзисторлық кілт 1. 1-суретте көрсетілген. Жаппасы триггерге қосылған

кілттік транзистор Т2 триггердің жағдайына байланысты ab аралығын

тұйықтайды немесе ажыратады.

БҚЖС-ны бағдарлау

жады

конфигурациясына сәйкесті деректерді енгізу арқылы жүргізіледі. Бұл кезде

таңдалым жолындағы (FL, Fetch Line) жоғарғы потенциал Т1 транзисторын

қосып, жазу-оқу жолындағы (WRL, Write/Read Line) сигнал триггерді сәйкесті

жағдайға қояды. Жұмыс режимінде транзистор Т1 жабық болады да, триггер

өзгермес жағдайын сақтайды.

15

1. 1 Сурет

Кілттік Т2 транзисторын (pass-transistor) бағдарланымды байланыс

нүктесі (PIP, Programmable Interconnection Point) деп атауға болады. Конфигу-

рациясы триггерлі жадымен берілген БҚЖС-ны қайта бағдарлау жұмыс

режимінде кодтар тізбесін триггерлер тізбесіне жазу арқылы жүргізіледі.

БҚЖС-ның жалпы қасиеттері туралы айта отырып, құрылымының

реттілігіне байланысты олардың аса жоғары деңгейлі жиналыммен жүзеге

асырылатындығын айта кету керек. GA құрылымдарынан ерекше, БҚЖС

құрылымдарында логикалық элементтермен қатар триггерлер мен т. б. және

олардың арабайланыстары да жүзеге асырылған. БҚЖС тұтынушысы ақырғы

операцияларды жүргізу үшін оларды жасаушыға байланыспай-ақ,

бағдарлауды өзі жүргізеді. Сондықтан бұндай микросұлбаларды стандартты

өнімге теңеуге негіз бар, ал бұл белгілі артықшылықтарға - өндірісте

шығарылу санының кеңейтілуіне және құнының кемуіне әкеледі.

PLA, PAL және GA микросұлбаларының құрылым негізін қалаған

идеялар мен олардың бағдарлану принциптері бағдарламалы және қайта

бағдарламалы құрылымды логикалық сұлбалардың негізгі даму бағыттарын

анықтады. GA бағытының жалғасы - FPGA (Field Programmable Gate Arrays),

ал PAL бағытының жалғасы CPLD (Complex Programmable Logic Devices) ЖС

болды. Бұл екі құрылымның артықшылық жақтарын біріктіру FLEX (Flexible

Logic Element MatriX) аталымды аралас архитектураның құрылуына әкелді.

Жиналым деңгейінің көтерілуі кристалда, күрделілігі жағынан түгел жүйеге

сәйкес келетін, SOC (Systems On Chip) деп аталатын, сұлбаларды

орналастыруға мүмкіндік берді.

1. 2 Вентилдік матрицалар

Вентилдік матрицалардың

(GA, Gate Array)

бастапқы үлгілері

жоғарыөнімді ЭЕМ-ларының стандартты емес сұлбаларын кіші және орта

деңгейлі жиналымды микросұлбаларсыз жүзеге асыруға құрал ретінде

шығарылғанды.

GA-ның бірінші ұрпағының

негізі

-

кристалда реттелімді

орналастырылған базалық ұяшықтардың (БҰ) жинағы, олардың араларында

байланыстар (арналар) құруға бос аймақтар қалдырылған. GA-ның ішкі

аймағындағы базалық ұяшықтардың құрамында бір-біріне жалғанбаған

элементтердің (транзисторлардың, резисторлардың және т. б. ) топтары, ал

кристалдың перифериялық аймақтарында, сұлбалық компоненттері GA-ның

16

сыртқы әлеммен байланысын жүзеге асыруға бағытталған, енгізу-шығару

ұяшықтары орналастырылған. Сонымен, GA-ны сәйкесті байланыстарды

жүзеге асыру арқылы қажетті сұлбаға айналдырылатын бастапқы дайындалым

ретінде қарастыруға болады.

GA түрлерін суреттеместен бұрын негізгі түсініктер мен анықтамаларға

тоқтай кетелік.

Базалық ұяшық (БҰ) кристалдың нақтылы аймағында реттелімді

қайталанатын

сұлбалық

элементтердің жинағы екендігі алдында

анықталғанды. GA-ның ішкі аймағындағы базалық ұяшықтар матрицалық -

базалық ұяшықтар

(МБҰ),

перифериялық аймақтың ұяшықтары

перифериялық базалық ұяшықтар (ПБҰ) деп аталады. GA ұяшықтарын

ұйымдастыруға екі тәсіл қолданылады:

− МБҰ элементтерінен бір логикалық элемент қалыптастыруға

болады, ал одан күрделірек қызметтерді жүзеге асыру үшін бірнеше ұяшық

пайдаланылады;

− МБҰ элементтерінен кез келген қызмет түйінін қалыптастыруға

болады, ұяшық элементтерінің құрамы ең күрделі түйіннің сұлбасымен

анықталады.

Қызмет ұяшығы (ҚҰ) - бір немесе бірнеше БҰ элементтерін жалғау

арқылы жүзеге асырылатын сұлба.

Қызмет ұяшықтарының қоры - GA негізінде жобалау кезінде

пайдаланылатын ҚҰ-лар жинамы. Құрамына көптеген (жүздеген) қызмет

элементтері, түйіндер және олардың жеке бөліктері кіретін, бұл қор GA-ның

жасалуы кезінде құрылады және олар ақырғы құрылғыны құрушыға бір

немесе бірнеше БҰ арқылы жүзеге асырылуға мүмкіндік беретін дайын

шешімдер ұсынады. Сұлбақұралыстық мәселелер қор құрылуы кезінде

шешілгендіктен, пайдаланушы қормен жұмыс істеу арқылы жобалауды

қызметтік-логикалық деңгейде жүргізеді.

Эквивалентті вентиль (ЭВ) - логикалық функцияны (әдетте екікірісті

ЖӘНЕ-ЕМЕС немесе НЕМЕСЕ-ЕМЕС элементін) жүзеге асыруға мүмкіндік

беретін, GA элементтерінің тобымен сипатталатын,

бағалауға арналған түсінік.

GA күрделілігін

Жол жүргізу

(трассировка)

арналары

-

GA

кристалындағы

арабайланыстар орналастыруға арналған кеңістіктер.

1. 2. 1 GA түрлері

Бастапқы, және классикалық ретінде қарастырылатын, арналы GA-ның

ішкі (орталық) аймағында базалық ұяшықтар мен жол жүргізу арналары

орналастырылған. Оларда байланыс құру мүмкіншілігі

жоғары, бірақ

элементтердің орналастырылым тығыздығы

(арабайланыстарға едәуір

кеңістіктің бөлінетіндігінен) кемдеу болады.

Арналы архитектура, үлкен энергия шашырамын қажет қылатын, бипо-

лярлы GA-ларға тән.

17

Арабайланыстар орналастыруға бөлінген аймағы кемітілген, жоғары

жиналымды GA құру жолын іздеу арнасыз GA архитектурасына әкелді.

Бұндай GA-ның ішкі аймағында тығыз орналастырылған базалық ұяшықтар

болады, бірақ арабайланыстар жүргізуге арналған арналар болмайды. Бұл

кристалдың БҰ орналасқан кез келген аймағын логикалық сұлба құруға да,

арабайланыстар құруға да пайдалануға болады. Арнасыз GA, элементтердің

орналастырылуы тығыз және энергия шашырамы аз болатын, КМТШ-

сұлбақұралысына тән.

GA кристалының перифериялық аймағында, сұлбалық компоненттері

енгізу-шығару жұмыстарын жүзеге асыруға бағытталған, арнайы ПБ-лар

орналасқан.

Өңделуші сигналдар түрі (цифрлық, аналогты) базалық ұяшықтардың

сұлбалық элементтерінің құрамына әсер етеді. Бұған бұған байланысты GA

цифрлық, аналогты және цифрлы-аналогты болып бөлінеді. Аналогты және

цифрлы-аналогты GA құрамында операциялық күшейткіштер, аналогты

кілттер мен компараторлар және т. б. құруға мүмкіндік береді.

Пайдаланылатын сұлбақұалысына

байланысты жіктеме GA-лардың

негізгі варианттарын ғана сипаттайды.

Максималды тезәрекеттілік

варианттары ЭБЛ түріндегі сұлбалармен жүзеге асырылады. КМТШ

сұлбақұалысы,

алдында айтылғандай, элементтердің орналастырылу

тығыздығын көтерілген және энергия шашырамы азайтылған микросұлбалар

құруға ыңғайлы. ТТЛШ сұлбақұалысының негізінде тезәрекеттілігі орташа

келетін GA жасалады.

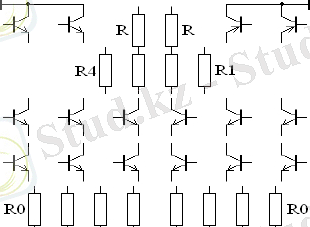

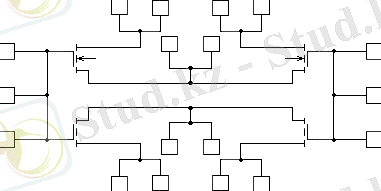

1. 2-суретте екіқатарлы логикалық элементтер жүзеге асыруға арналған

ЭБЛ түрлі GA-ның БҰ-ның құрамы көрсетілген. Ондағы R0 резисторларын

параллель немесе тізбелеп қосу арқылы тезәрекеттілігі мен тұтынатын қуаты

әртүрлі сұлбалар құруға болады.

1. 2 Сурет

1. 3-суретте КМОП түрлі GA-ның БҰ-ның бір варианты келтірілген.

Оның сұлбалық элементтері ретінде с р- және n-арналы транзисторлар ғана

18

пайдаланылады. Суретте 4 транзисторлы ұяшық сұлбасы көрсетілген. Транзи-

сторларды тізбе немесе параллель жалғау арқылы ЖӘНЕ-ЕМЕС және

НЕМЕСЕ-ЕМЕС логикалық элементтерінің сұлбаларын жүзеге асыруға

болады.

Ұяшықтарды күрделендіру қарапайым ұяшықтарды біріктіру арқылы

жүргізіледі.

1. 3 Сурет

1. 3 Пайдаланушы бағдарлайтын вентилді матрицалар

Пайдаланушы бағдарлайтын вентилді матрицалар

(FPGA, Field

Programmable Gate Arrays) топологиясы жағынан арналы GA құрылымдарына

ұқсас келеді. Олардың ішкі аймағында, араларында жол жүргізу арналары

ескерілген, көптеген бірдей құрылымды, конфигурацияланатын логикалық

блоктардың (LB, Configurable Logic Block) реттелген жинамы, ал кристалл

перифериясында

енгізу/шығару блоктары (IOB, Input/Output Blocks)

орналасқан.

FPGA қасиеттері мен мүмкіндіктері алдымен олардың құрамындағы LB

сипатына және арабайланыс жүйесіне байланысты.

1. 3. 1 FPGA құрамындағы логикалық блоктар

FPGA құрамындағы LB ретінде келесі құрылымдар пайдаланылады:

− транзистор жұптары;

− қарапайым логикалық ЖӘНЕ-ЕМЕС, НЕМЕСЕ-ЕМЕС вентилдері

(SLC, Simple Logic Cells) ;

− мультиплексорлар негізіндегі логикалық модулер;

− PROM негізіндегі логикалық модулер (LUT, Look-Up Tables) .

LB-ның маңызды сипаттамаларына оның “түйіршіктілігі” (Granularity)

мен

“іскерлігі” (Functionality)

жатады.

Біріншісі

қажетті сұлбалар

“жиналатын” бөліктемелердің “уақтылығы” қандай болатындығымен, ал

екіншісі LB-ның логикалық мүмкіндігінің қаншама үлкен болатындығымен

байланысты.

19

LB-ның уақтүйіршіктілігі шығарылатын функцияларды әртүрлі тәсілмен

жүзеге асыруға кең мүмкіндік береді, бірақ кристалда бағдарламалы байланыс

нүктелерінің көп болатындығынан, ол FPGA-ның арабайланыс жүйесін

күрделендіреді.

Ірітүйіршікті LB-ларда күрделірек функциялар жүзеге асырылады,

сондықтан арабайланыс бағдарлануын жеңілдетеді. Триггерлі жадымен

реконфигурациялатын FPGA-да, әдетте, ірітүйіршікті блоктар қолданылады.

р- және n-арналы транзисторлар тізбесі түрінде құрылған, ал олардың

арасына жол жүргізу арналары орналастырылған, ең уақтүйіршікті LB

Crosspoint Solutions фирмасының микросұлбаларында пайдаланылады (1. 4-

суретті қара) .

Өткізгіштігі

әртүрлі транзистор

жұптарынан

КМТШ-

сұлбаларындағы жиналым тәсілдері дәстүрлі,

жиналады.

1. 4 Сурет

логикалық

элементтер

1. 5,

а -суретте

F = x1x2Vx3x4

функциясын жүзеге асырушы

... жалғасы- Іс жүргізу

- Автоматтандыру, Техника

- Алғашқы әскери дайындық

- Астрономия

- Ауыл шаруашылығы

- Банк ісі

- Бизнесті бағалау

- Биология

- Бухгалтерлік іс

- Валеология

- Ветеринария

- География

- Геология, Геофизика, Геодезия

- Дін

- Ет, сүт, шарап өнімдері

- Жалпы тарих

- Жер кадастрі, Жылжымайтын мүлік

- Журналистика

- Информатика

- Кеден ісі

- Маркетинг

- Математика, Геометрия

- Медицина

- Мемлекеттік басқару

- Менеджмент

- Мұнай, Газ

- Мұрағат ісі

- Мәдениеттану

- ОБЖ (Основы безопасности жизнедеятельности)

- Педагогика

- Полиграфия

- Психология

- Салық

- Саясаттану

- Сақтандыру

- Сертификаттау, стандарттау

- Социология, Демография

- Спорт

- Статистика

- Тілтану, Филология

- Тарихи тұлғалар

- Тау-кен ісі

- Транспорт

- Туризм

- Физика

- Философия

- Халықаралық қатынастар

- Химия

- Экология, Қоршаған ортаны қорғау

- Экономика

- Экономикалық география

- Электротехника

- Қазақстан тарихы

- Қаржы

- Құрылыс

- Құқық, Криминалистика

- Әдебиет

- Өнер, музыка

- Өнеркәсіп, Өндіріс

Қазақ тілінде жазылған рефераттар, курстық жұмыстар, дипломдық жұмыстар бойынша біздің қор #1 болып табылады.

Ақпарат

Қосымша

Email: info@stud.kz