Микропроцессорлық жүйенің архитектурасы, жады ұйымдастыруы және блоктарды модельдеу

МАЗМҰНЫ

КІРІСПЕ . . .

I МИКРОПРОЦЕССОРЛЫҚ ЖҮЙЕ . . .

- Микропроцессор және микрокомпьютер . . .

- Микропроцессордың типтік құрылымы . . .

- Есте сақтау құрылғысы . . . Еркін қол жеткізу. Есте сақтау құрылғысын ұйымдастыру . . . Екі өлшемді адресация . . . Біркелкілік жады . . . Есте сақтау тізбектік кіріс . . . Стектер . . .

- Арифметикалық құрылғы . . .

- Басқару құрылғысы . . .

- Енгізу - шығару құрылғысы . . . Енгізу - шығару порттары . . .

- Шиналар . . .

1. 8 Технологиялық комплекстердің автоматизация жүйелерінде

бағдарламаланатын контроллер . . .

1. 8. 1 Микроконтроллер архитектурасы . . .

1. 8. 2 Бағдарламалық қамтамасыздандыру құрылымдары . . .

1. 8. 3 Беруші құрылғы ретінде бағдарламаланатын контроллер . . .

1. 8. 4 Беріліс функциялары және интерполяция. Интерполяцияның

дәлдігі . . .

- Басқарудың көпконтурлы құрылғысы ретінде микроконтроллер . . .

- Берілетін сигналдардың дискретизациясы.

Котельников теоремасы . . .

1. 8. 7 Берілген сигналдарды деңгей бойынша кванттау . . .

II МП ЖҮЙЕСІНДЕГІ БЛОКТАРЫН МОДЕЛЬДЕУ . . .

2. 1 Енгізу - шығару құрылғысы . . .

2. 2 Оперативті есте сақтау құрылғысы . . .

ПАЙДАЛАНҒАН ӘДЕБИЕТТЕР . . .

МИКРОПРОЦЕССОРЛЫҚ ЖҮЙЕ

- Микропроцессорлар және микрокомпьюторлар

Электронды құралдардың функциялық мүмкіндігін кеңейтуге және оның сандық және саналық көсеткіштерінің, жақсаруы 10-15 тен 25-100-ге дейінгі тізбектік элементтерінен тұратын интегралдық микросхема пайда болуымен байланысты. Микроэлектрониканың одан әрі дамуы 1000 және 1-ға дейінгі компанеттерден тұратын үлкен интегралды схемаларды құрастыруға бағытталған. Жартылай өткізгіш кристаллындағы компанентінің санын N, микросхемалар интеграцияларының дәрежесін R- көрсетеді. Оны келесі формуламен анықтайды.

R=lgN

Осы формула негізінде интеграцияның бірінші дәрежесі ретінде 10 компанетқа дейінгі микросхемалар.

Екінші дәрежеге 11- ден 100-ге дейінгі.

Үшіншіге 101-1000-ға дейінгі және тағы басқа қабылданған. Үлкен интегралды схемалардың пайда болуы интегралды компаненттерден элекронды құрылғылар өндірісімен нақты бірігуі басталады. Үлкен интегралды схема сандық құрылғылардың есептегіш, тіркеуші, дешифраторлы тағы басқа құрылғылары бір қатар типтік түйіндермен тізбектерін көрсетеді. Олардың негізінде блоктар және де бүтіндей электронды құрылғылар іске асырылады.

Микропроцессор- үлкен интегралды тізбек технологиясы негізінде жасалған бағдарламаланатын саналық құрылғы.

Микропроцессор құрылымында үлкен иірімділік орнатылған. Өздігімен ол қандай да бір нақты мәселені шеше алмайды. Мәселені шешу үшін оны программалап, басқа құрылғылармен байланыстыру керек. Оның құрамына негізінен есте сақтау және енгізу- шығару құрылғылары кіреді. Микрокомпьютер немемсе микропроцессорлық жүйе деген, ол жалпы алғанда қандайда бір нақты қызметті атқаруға көзделген бір- бірімен байланысқан микропроцессор есте сақтау, енгізу- шығару жүйелік құрылғылардың үйлесімділігі.

Микрокомпьютерлер қарапайым электронды есептеу машина қасиеттерінен олардың басты айырмашылығы, оның құнының арзандылығы және өте кішкентай өлшемі. Осы қасиеттеріне байланысты олар кең қолдануда.

1. 2 Микропроцессордың типтік құрылымы

Гинотикалық микропроцессордың жалпы құрылыма кіретін компоненттер оның бағдарламалық басқару процессоры болып табылады. Кейбір компаненттер, яғни программалық санағыш, стек және командалар регистрі командаларды өндеу үшін арналған. АЛУ, триггерлік көшіру, ортақ регистрлер ( жұмыс регистрі) және мәліметтердің адрес регистрі сияқты компаненттер мәліметтерді өндеу үшін арналған. Барлық қалған компаненттер, яғни командалар дешифраторы және басқару және синхронизация блогы, басқа компаненттердің жұмысын басқарады. Компаненттердің өз ара әсерлесуі мәліметтердің ішкі беріліс каналы арқылы орындалады. Микропроцессордың басқа блогтармен( ЕСҚ және енгізу- шығару құрылғылармен) байланысы адрестік шина, мәліметтер шинасы және басқару шина бойынша орындалады.

Микропроцессор 8 биттен тұратын сөздер мен жұмыс істейді. Байт деп аталатын мұндай сөздер арифметикалық және логикалық операцияларды орындағанда ынғайлы және шығарылатын микропроцессордың көбінде қолданылады.

Микропроцессорға және микропроцессордан ақпарат шиналар арқылы беріледі. Мәліметтер шинасы сөздің ұзындығына сәйкес 8 желіден, ал адрестік шина 16 желіден тұрады. Адрестік шина бірбағытты, ал мәліметтер шинасы екібағытты болады. Басқар ушинасы басқару және синхронизация блогына апаратын 5 желіде және одан шығатын 8 желіден тұрады. Бұл желілер арқылы микропроцессор компаненттері арасында және микропроцессормен микрокомпьютердің басқа блогтары арасында басқарушы және тактылы сигналдар беріледі.

Командалар санағышы 16 биттен тұрады және жадыдан оқылатын команданың келесі байтына адресін құрайды. Әр байтты оқығаннан кейін ол автоматты түрде бір бірлігіне үлкейеді. Командалар санағышы және 64 регистрлі стек төбесі арасында байланыс болады. Стектің функциясының бірі- подпрограммадан қайтару адресін сақтау. Сонымен қатар стекте жоғапғы үш жалпы регистрлерден және көшіру тригерінен мәліметтер сақталуы мүмкін.

Мәліметтер сөзі бір байттан тұратын болса, команда бір, екі немесе үш байттан тұруы мүмкін.

Кез-келген команданың бірінші байты мәліметтер шинасы бойынша жадыдан командалар регистріне өтеді. Бұл бірінші байт оның мағынасын анықтайтын командалар дешифраторлар кірісіне беріледі. Негізінен дешифратор командасы бір байтты немесе одан көп байт санынан тұратындығын анықтайды. Соңғы жағдайда қосымша байттар мәліметтер шинасы арқылы жадыдан беріледі және мәліметтер адресі регистрінде және жалпы регистрдің бірінде қабылданады.

1. 3 Есте сақтау құрылғысы

Есте сақтау құрылғысы немесе жады - бұл құрылғы, ол арқылы ақпарат уақыт бойынша бар болады, дәлірек, бір моменттен екіншісіне беріледі. Беріліс бағыты нақты уақыт қозғалыс бағытымен сәйкес келеді, ал нақтырақ алға қозғалысымен. Сондықтан, есте сақтау құрылғысы нақ осы уақытты түзетілген ақпаратты болашаққа тасымалдауға мүмкіндік беретін арна ретінде түсінуге болады. Сонымен бірге барлық тізбекті схемалар және компьютерлер есте сақтау қасиеттеріне ие және бұл алдыңғы моменттерде кірістерден қазіргі моментке олардың кірістерінің тәуелді болуына мүмкіндік береді. Жалпы айтқанда, бұл сұлбаның қасиетіне есте сақтау құрылғысына маңызды, мысалы триггерлерге бұл тарауда біздің назарымыздың ортасында кейбір реттеуіш құрылымымен есте сақтау элементтерінің үлкен санынан тұратын есте сақтау құрылғылары болады.

Есте сақтау құрылғысының ұйымдастырылуы ақпараттық құрылғыға және одан тасымалданулар тәсілдерін анықтайды. Әдетте ақпарат биттерінің белгіленген санынан тұратын және сөздер деп аталатын бөліктермен тасымалданады. Есте сақату құрылғысын сөздің орналасуы үшін көптеген ұқсастырылыған орындалған тұратын кейбір кеңістік түрде келтіруге болады.

Кейбір есте сақату құрылғысы мұндай орынның әр қайсысына өзіндік белгіленген есте сақтау элементтері беріледі. Бұл жағдайда есте сақтау элементтерінің орналасу жері ұяшық деп аталатын сөз орнын анықтайды. Басқа есте сақтау құрылғысындағы сөздер бір-біріне қатысты ретке келтірілулігін есте сақтап, есте сақтау элементтерінің көптігіне қатысты орналасады. Бұл жағдайда сөз орны уақытпен және сол сияқты есте сақтау элементтерінің орналасуымен ұқсастырылады. Барлық жағдайларда, ақпарат есте сақтау құрылғысына берілгенде, ол кейбір нақты орынға орналасады. Бұл процесс жадқа жазу деп аталады. Басқаша айтқанда, жадыдан ақпарат тасымалданғанда, ол сол сияқты кейбір нақты орыннан таңдалады (әдетте ақпарат осы орында сақталады) . Бұл процесс жадыдан оқу деп аталады.

Сол орынды таңдаудың түрлі әдістері бар, олар үшін жазу немесе оқу операциясы дайындалады. Орынды таңдау және ақпаратты орнына немесе сыртқа тасымалдау құралы қатынау құралын құрады (немесе таңдамаларды) . Есте сақтау құрылғысы екі басты түрлерге бөлінеді: бос қатынаумен есте сақтау құрылғысы және тізбектей қатынаумен есте сақтау құрылғысы. Бірініші түрге кез келген орынға шамамен бірдей уақытта қажет ететін қатынауы болатын есте сақтау құрылғысы жатады. Басқа сөзбен айтқанда, біз кездейсоқ түрге орын таңдай аламыз, ол оқу немесе жазуға кететін уақытқа әсер етпейді. Екінші түріне тек белгілі бір ретпен қатынауы болатын есте сақтау құрылғысы жатады. Кейінгі бөлімдерде біз екі аталған типтегі есте сақтау құрылғыларын қарастырамыз.

1. 3. 1 Еркін қол жеткізу. Есте сақтау құрылғысын ұйымдастыру

Еркін қол жеткізуі бар жады - бұл ұяшықта сақталған дерек элементі тікелей оқылатын есте сақтау құрылғысы. Берілген ұяшықты таңдау үшін қажетті уақыт шамамен басқа ұяшықтар үшін кететін уақытпен бірдей болады. Әрбір ұяшық есте сақтау элементтерінің белгіленген саны мен өзінің ұқсас номерінен тұрады. Биттердің белгіленген санынан тұратын ұқсастырушы номер ұяшық адресі деп аталады. Адрестердің бар болуы жазу және оқу операцияларының орындалуы үшін ұяшықтарға қатынау кезінде оларды ажыратуға мүмкіндік беред.

Жалпы жағдайда бос қатынаумен есте сақтау құрылғысы бірнеше блоктардан немесе модульдерден тұрады. Жартылай өткізгішті жадылар үшін әдетте модульдер жеке интегралды схемалар түрінде жүзеге асырылады. Сыртқы сигналды сызықтардың құрамы мен қызметтері құр ұйымдастырылуы мен жүйеде байланыстардың жұмысын жеңілдететіндей есеппен таңдалады. Мұндай сызықтар санына сөз адресін тапсыратын сызықтар, оларға қатынасу жүргізіледі, деректерді модульдерге немесе модульден тасымалдану сызықтары және керекті операцияны тапсыруға мүмкіндік беретін (жазу немесе оқу) бірнеше басқару сызықтары жатады.

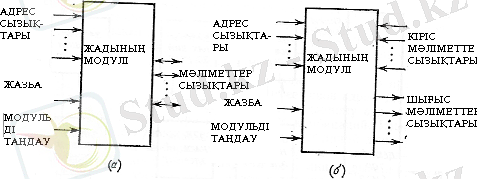

Құрлардың түрлі типтеріне сәйкес келетін сыртқы сигналдарының жинақталуымен модульдердің көптеген түрлері болады, бірақ модульдердің көпшілігін 1суретте көрсетілген негізіг модульдердің біреуіне жатқызуға болады. Олар тек деректер сызықтарымен ажыратылады. 1(а) -суреттегі модульде деректер сызықтар жиынтығынан тек біреуі болады, олар бойымен жазу кезінде түсетін деректер сол сияқты оқу кезінде шығарылатын деректер беріледі. 1(б) -суреттегі модуль келетін және шығарылатын деректер үшін арналған екі түрлі сызықтар жиынтығынан тұрады.

1-сурет. Бос қатынау жады модуліндегі сыртқы сигналдар сызықтары (а) . Модуль мәліметтердің екібағытты сызықтарымен (б) . Модуль келетін жіне жіберілетін мәліметтердің жеке сызықтарымен.

Екі модульдер адрестік сызықтар жиынтығынан тұрады, олардың сигналдары деректерді оқу және жазу үшін қатынасуы жүзеге асатын анықтайды. Екі модульдерде де “жазу” басқарушы сызығы жазу режимін тапсырады (“жазу”=1) немесе оқу режимін (“жазу”=0) тапсырады. Соңында “модуль таңдамасы” басқарушы сызығы екі жағдайда берілген модульде не оқу /жазу операциялардың орындалуын шешеді (“модуль таңдамасы”=1), не оның орындалуын рұқсат етпейді (“модуль таңдамасы”=0) .

Екі модульдердің кез келгеніне сәйкес келетін жады модулін көп модульді құр ұйымдастыруымен есте сақтау жүйесіне қосу үшін деректерді беретін сызықта, яғни 1(а) -суреттегі модульдердің деректер сызығында және 1(б) -суреттегі модульдердің шығыс деректер сызығында құрастыру лгикасын жіберетін вентильдер қолданылады. Кез келген модульдегі жады модулі шығыс сызықтарына деректерді тек оқылу кезінде береді: барлық қалған жағдайларда бұл сызықтармен сызықтарға жалғанған жадының басқа модульдері немесе құрылғылары қолдана алады. Бұл 1(а) -суреттегі жағдай үшін ерекше маңызды, себебі есте сақтау құрылғысы деректерді жіберу үшін оқылу кезінде сол сызықтар қолданылуы тиіс.

Модульде оқу орындалмағанда шығыс деректер сызықтардың жағдайлары құрастыру логикасының түріне тәуелді. Мысалы құрастырылмалы ЖӘНЕ үшін ашық коллекторлы ТТЛ схемаларында бос жолдағы жағдай логикалық 1 сәйкес келуі тиіс, себебі бұл жағдайда 0 1-ң үстінен (доминирует) және соған сәйкес жадының басқа модулі мен құрылғысы сызықта оған қажетті жағдайды тапсыра алады. Құрастырулы НЕМЕСЕ үшін бос жағдай логикалық 0 болуы керек. Үш орнықты құрастыру логикасы үшін бос жағдай бұл жоғары инпедансымен үшінші жағдай, сызықпен баламалы қосылысының болмауы кез келген жағдайда не “жазу” сызығына логикалық 1 берілгенде, не “модуль таңдауы” сызығына логикалық 0 берілгенде шығыс деректерінің сызығы бос жағдайына түседі.

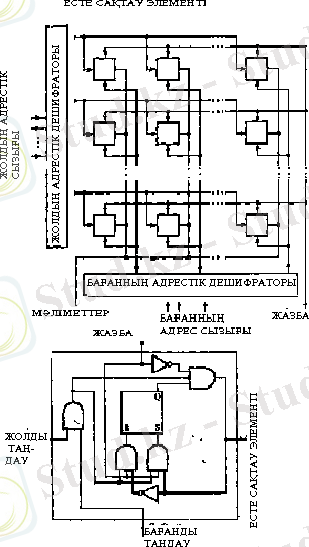

Бос қатынаумен есте сақтау құрылғысының ішкі ұйымдастырылуы жадының бос қатынауымен типті модульдердің сыртқы сипаттамаларын қарастырғаннан кейін, енді олардың ішкі ұйымдастыруына өтейік. Қажетті ұяшықты таңдауға және оның ішіне немесе одан ақпараттың тасымалдануының жүзеге асырылуына мүмкіндік беретін бүкіл схемалардың бірі 2-суретте келтірілген.

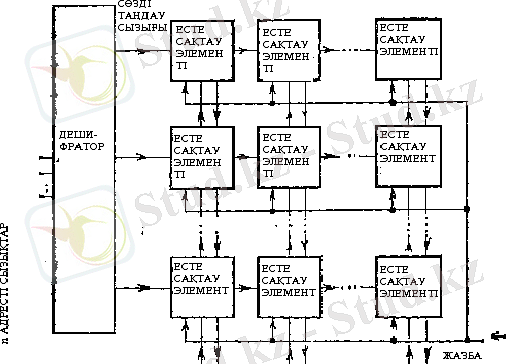

2 сурет. Бос қатынау жады модулінің ішкі ұйымдастырылуы.

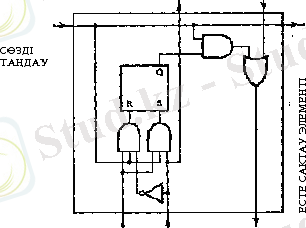

Есте сақтау элементінде сөздің бір битінің сақталуы үшін асинхронды RS-триггер қолданылады. Триггерден басқа, әрбір есте сақтау элементі триггер мен деректердің ішкі сызықтары арасынан ақпараттың тасымалдануы үшін вентильдерден тұрады.

Оқу немесе жазу, екі операциялардың бірі. Бір “қатардың” барлық элементтері үшін бір уақытта орындалады. Әрбір “қатар” сөзді сақтау үшін ұяшықтан тұрады және оның өз адресі болады. “2 n ден 1” дешифраторы берілген адрес бойынша ұяшықтың таңдалуы үшін қызмет етеді. Негізінен оларға керекті ұяшық адресі беріледі. Дешифратордың 2 n шығыс сызықтары сөз таңдама сызықтары деп аталады. Дешифратор кірісіне берілген комбинациясынан тәуелділікте сөз таңдамасының қандайда бір сызығы логикалық 1 мәнін алады, ал қалған барлығы - логикалық 0. сөз таңдама сызықтарының әр қайсысы қатарлардың барлық элементтерінде оқу немесе жазу операцияларын шешетін сызық ретінде қолданылады.

Әрбір бағанда екі ішкі сызықтар болады: біреуі - жадыда деректердің берілісі үшін (кіріс), ал екіншісі - жадыдан (шығыс) . “Шығыс” сызығының жағдайы таңдалған қатардағы есте сақтау элементімен анықталады. Ол үшін әрбір элементте триггер шығысы логикалық түрде “сөз таңдамасы” сигналына көбейтіледі, ал барлық нәтижелердің логикалық қосындысы шығым сызығына келеді. Осылайша, жадыдан сөздің оқылуы дешифратор кірісіне қапсетті сөз адресінің берілуімен және “шығыс” сызығында жағдайды қадағалаумен орындалады.

Әрбір бағанның “кіріс” сызығы жазу оперциясы орындалу кезінде таңдалған қатарлардың есте сақтау элементіне ақпараттың берілуі үшін қолданылады. Бұл әрбір есте сақтау элементіне екі және вентильтердің көмегімен жүзеге асырылады. Олар “сөз таңдауы” және “жазу” сигналдарының бар болуы кезінде “кіріс” сызығынан S триггер кірісіне сигналды тасымалдайды, ал оның қосымшасын - R кірісіне береді. Осылайша, жадыға сөздің жазылуы дешифратор кірісінде қажетті ұяшықтың адресін тапсырумен орындалады, ал жазылатын сөздің - “кіріс” сызығында және кейіннен - “жазу” басқару сызығында логикалық 1.

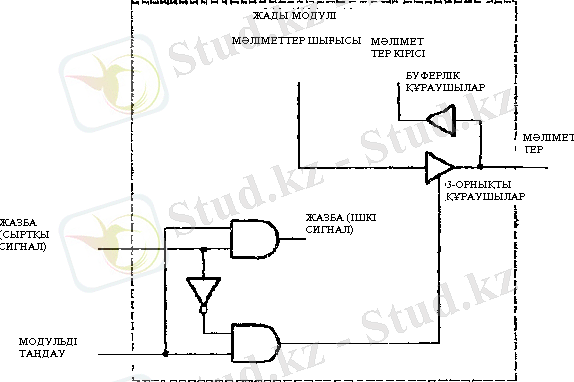

Жоғарыда келтірілген түсініктемеде жады модулі үшін ішкі болып табылатын “жазу”, “кіріс” және “шығыс” сызықтарында сигналдар бейнеленді. Бұл сигналдар модульге қатысы бойынша сыртқы сигналдармен сәйкес келетін вентильдер мен буферлік схемалардың көмегімен байланысқан. Мұндай байланыс модульдің керекті сыртқы сипаттамаларынан тәуелділікте түрлі тәсілдермен жүзеге асырылады.

Мысалы, 1(а) -суреттегі модульдің сыртқы сипаттамаларын 3-суреттегі схемалар көмегімен алуға болады. Ол жерде үш сыртық сызық: “жазу”, “модуль таңдауы” және “деректер”. Ішкі “жазу” сигналы сыртқы “жазу” және “модуль таңдамасы” сигналдарынан ЖӘНЕ ретінде алынады. Суретте көрсетілгендей, сыртқы “деректер кірісі” және “жазу” сызықтары сөздей әр бит үшін “деректер ” сыртқы сызығымен ішкі буферлік схемасы және үшорнықты шығыс құрушысы арқылы қосылады. Үшорнықты құрушысы “модуль таңдамасы” сигналынан және “жазу” сигналының терісінен ЖӘНЕ сигналымен басқарылады. Осылайша, деректердің сыртқы сызығы жазу кезінде деректердің кіріс сызығына ақпаратты беріп және оқу кезінде деректердің шығыс сызығынан ақпаратты қабылдай отырып, екі бағытты түрінде жұмыс жасайды.

3-сурет. Жады модулінде сыртқы және ішкі сигналдар арасында байланыс.

- Екі өлшемді адресация.

Қарастырылған бос қатынау есте сақтау құрылғысы схемасының кемшілігі адрестік дешифратордың үлкен өлшемімен байланысты. Мысалы, n=10 кезінде адрестік дешифраторды 2 10 =1024 шығыс болуы керек. Әрбір шығыс қатарда есте сақтау элементімен қосылуы тиіс. Байланыс санын азайтуға болады, егер дешифратор функциясының бір бөлігін есте сақтау элементіне беретін болсақ.

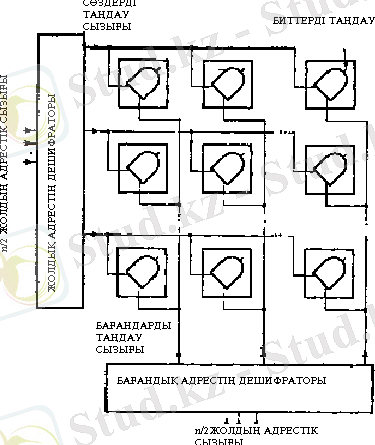

Бұл қалай жасалатынын көрсететін болсақ, 2 суретте келтірілген есте сақтау құрылғысы ұйымдастыруымен бір бағанын аламыз және одан тік бұрышты матрицасын құрастырамыз. n=10 кезінде есте сақтау элементтерінің саны 2 10 -не тең. 2 5 х2 5 өлшемді матрицаны немесе жалпы жағдайда 4 суретінде көрсетілгендей 2 m х 2 n-m матрицасын құруға болады. Шығыс бағанының әр элементі тік бұрышты матрицаның қатары мен баған қиылысында жатыр.

4 сурет. Бос қатынау ЕҚ-дағы екіөлшемді адрестеу.

Әрқайсысында n/2 кіріс және 2 n/2 шығыс сызықтары бар 2 дешифратор алайық. (n тақ және квадраттық матрица деп алайық) . n =10 кезінде 2 n/2 саны 32-ге тең. Бір дешифратордың шығыс сызықтары қатар таңдамасы үшін қызмет етеді, ал басқалары - матрица бағаның таңдауы үшін. Мұндай әдіс кезінде дешифратордағы шығыс сызықтарының жалпы саны 2 n/2 +2 n/2 =2 n/2 +1, ол бір адрестік дешифратор кезінде 2 n сызығынан едәір кіші болады.

Әрбір есте сақтау элементінде баған мен қатар таңдау сызықтарының үстінде ЖӘНЕ операциясы орындалуы тиіс. Бұл операциясы баған мен қатар қиылысында орналасқан тек бір элемент үшін логикалық 1-ді береді, ал барлық қалған элементтер үшін - логикалық 0, себебі олар үшін не баған таңдау сигналы, не қатар таңдау сигналы 0-ге тең болады. ЖӘНЕ вентилінің шығыс сигналы бит таңдау сигналының қызметін орындайды, ол берілген элементте оқу немесе жазуды шешеді.

Ұқсас екіөлшемді матрицалар сөздегі барлық қалған биттер үшін қажет. Матрицаларды параллель кеңістіктерде жатушы деп есептеуге болады. Адрестік дешифратордың екеуі де дереу бүкіл кеңістікте жұмыс жасайды, осылайша, ұяшықтың барлық биттері бір уақытта адрестеледі. Осы кезде дешифраторлардағы шығыс сызықтарының санының үлкеймейтіндігіне назар аудару керек.

Ішкі екібағытты шинасы бар есте сақтау құрылғысы.

Бос қатынау жады модуліндегі ішкі байланыстар санының төмендеуін деректердің ішкі кірістік және шығыстық сызықтар есебімен алуға болады, олар 2 суретте көрсетілген. Ол үшін сөздің әр битінің деректер сызығының екеуі де бір бағытты сызықпен ауысады. Жазылу кезінде ақпарат осы сызық бойымен таңдалған ұяшыққа тасымалданады. Оқылу кезінде ақпарат таңдалған ұяшықтан осы сызыққа беріледі. Мұнда алдыңғы тарауда келтірілген, құрларға арналған құрастыру логикасы мен оның қолданылуы толығымен қолданбалы. Құрастыру логикасын қолдану 5 суретте көрсетілген схемадағы есте сақтаудың әр элементінде бар және бағандарының барлық элементтерін деректердің шығыс сызығымен байланыстыратын НЕМЕСЕ вентильдердің керек болмауы есебінен қосымша үнемділікті алуға мүмкіндік береді.

Жадының мұндай модуль схемасы 5 суретте келтірілген. Сол суретте екіөлшемді адрестеу үшін және деректердің екібағытты сызықтардың біреуімен жұмысы үшін қажетті, өзгерістері бар есте сақтау элементінің логикалық схемасы келтірілген. “Жазу” сигналы деректер сызығы бойымен өтетін беріліс бағытын анықтайды. “Жазу” сызығындағы логикалық 1 алдыңғыдай, таңдалған ұяшықтың есте сақтау элементіне деректер берілісін шешеді. Бұл әр есте сақтау элементіне ЖӘНЕ вентилін қамтамассыз етеді, олардың кірістеріне үш сигнал беріледі: “жазу” терістігі, “бит таңдауы” және триггер шығысы. Мұнда құрастырушы НЕМЕСЕ-ні алуға мүмкіндік беретін арнайы ЖӘНЕ вентілі қолданылады. ЖӘНЕ вентілдер шығыстарының деректер сызықтарымен қосылысы осы шығыстардың құрастырушы НЕМЕСЕ береді.

5 сурет. Мәліметтердің екіөлшемді адресациясы және екібағытталған сызықтары бар ЕҚ.

- Біркелкі жады.

Біркелкі жады компьютерлер мен басқа цифрлық жүйелерле өзгермейтін ақпарат көзі болып қызмет етеді. Мысалы ретінде тұрақтылар тізімдері, деректерді түрлендіру үшін кесте және тұрақты программалар қызмет етеді. Мұндай жағдайларда жадының модульдері қолданылады, оларда жүйенің өзіндік қолданылатын модуль құралдарымен жазылған ақпаратты өзгерту мүмкін емес. Мұндай модульдерді өндіреді және тұрақты ЕҚ(ТЕҚ) немесе ROM типтегі жады(Read- Only Memory- тек оқылу жадысы) деп аталады. Өзгермейтін ақпаратты сақтау үшін ТЕҚ қолдану кейбір қолданбаларда едәуір артықшылықтарды береді, себебі ақпарат тоқ көзін өшіргенде де бұзылмайды. Одан басқа, ТЕҚ ақпарат жинақталуының үлкен тығыздығына жетуге болады, себебі есте сақтау элементтері заттай қарапайым.

ТЕҚ- ң базалық құрылымын адрес дешифраторынан және оған қосылған НЕМЕСЕ вентилдердің жиынтығынан тұрады деп түсінуге болады, 6- суретінде көрсетілгендей НЕҚ үшін сияқты, дешифратордың шығыс сызықтары ТЕҚ ұяшықтарымен өзарабірлік арақатынасында болады. НЕМЕСЕ вентилдерінің саны сөз разрядтығымен анықталады. Жадының кейбір сөзіне сәйкес келетін дешифратордың шығыс сызығын кейбір НЕМЕСЕ вентилінің кірісімен қосып, осы сөзде 1-ге тең бір бетінің мәнін тапсырамыз, кері жағдайда бұл мән 0- ге тең болады. Сонымен мысалы, 6- суреттегі сөздің бірінші, екінші және соңғы разрядтарында 0 адресті 10 . . . 1, адресті сөз 01 . . . 1 құрайды. Ал 2 n-1 адрестегі сөз 11 . . . 0 құрайды.

... жалғасы- Іс жүргізу

- Автоматтандыру, Техника

- Алғашқы әскери дайындық

- Астрономия

- Ауыл шаруашылығы

- Банк ісі

- Бизнесті бағалау

- Биология

- Бухгалтерлік іс

- Валеология

- Ветеринария

- География

- Геология, Геофизика, Геодезия

- Дін

- Ет, сүт, шарап өнімдері

- Жалпы тарих

- Жер кадастрі, Жылжымайтын мүлік

- Журналистика

- Информатика

- Кеден ісі

- Маркетинг

- Математика, Геометрия

- Медицина

- Мемлекеттік басқару

- Менеджмент

- Мұнай, Газ

- Мұрағат ісі

- Мәдениеттану

- ОБЖ (Основы безопасности жизнедеятельности)

- Педагогика

- Полиграфия

- Психология

- Салық

- Саясаттану

- Сақтандыру

- Сертификаттау, стандарттау

- Социология, Демография

- Спорт

- Статистика

- Тілтану, Филология

- Тарихи тұлғалар

- Тау-кен ісі

- Транспорт

- Туризм

- Физика

- Философия

- Халықаралық қатынастар

- Химия

- Экология, Қоршаған ортаны қорғау

- Экономика

- Экономикалық география

- Электротехника

- Қазақстан тарихы

- Қаржы

- Құрылыс

- Құқық, Криминалистика

- Әдебиет

- Өнер, музыка

- Өнеркәсіп, Өндіріс

Қазақ тілінде жазылған рефераттар, курстық жұмыстар, дипломдық жұмыстар бойынша біздің қор #1 болып табылады.

Ақпарат

Қосымша

Email: info@stud.kz