Pentium MMX микропроцессорының микроархитектурасы, MMX блогы және ішкі бүркеме-жады мен регистрлер жүйесі

КУРСТЫҚ ЖҰМЫСТЫ ОРЫНДАУҒА ТАПСЫРМА

Студент: Дандыбаев М. Б.

Тақырыбы: Pentium MMX микропроцессоры.

Аяқталған жұмысты тапсыру уақыты: «___»2005 ж.

Жұмыс барысында қолданылатын бастапқы мәліметтер мазмұны, жұмысты сипаттайтын негізгі бөлім қорытынды.

Жұмыс жетекшісі: Өнгенбаева Ж. Ж.

Тапсырманы орындауға қабылдап алған студент: Дандыбаев М. Б.

«___»2005 ж.

Мазмұны

Кіріспе

Негізгі бөім

1. Pentium микропроцессорларының микроархитектурасы

2. Ішкі бүркеме-жады

3. Регистрлер

3. 1. Жалпы мақсатты регистрлер

3. 2. Сегменттік регистрлер

3. 3. Күй және басқару регистрлері

4. Кеңейтілген командалар жүйелері

4. 1 SIMD-командалары

4. 2 SPFP - командалары

5. Pentium MMX процессоры

5. 1 ММХ блогы

5. 2 ММХ операциялық блогының командалары

6. Қорытынды

7. Қолданылған әдебиеттер

8. Қосымша А

Кіріспе

1971 жылы Intel фирмасының бірінші микропроцессорды жасап шығару компьютер дәуіріне бастама болды. Ширек ғасыр ішінде микропроцессор өте үлкен жетістіктерге жетті. Intel 404 бірінші типі 750 кГц жұмыс істеді және 2300 транзистордан тұрды. Оның өнімділігі секундына 60 мың операциямен бағаланды.

Бүгінгі таңда ең жақсы микропроцессор alpha 21264микропроцессоры болып саналады. Ол 7000 кГц жиілікте жұмыс істейді және 15. 2 млн. транзистордан тұрады. Секундына 2 млрд. операция орындайды.

Микропроцессор ең күрделі микроэлектрондық құрылғы. оған ғылыми және инженерлік жаңалықтар, ең соңғы жетістіктер енгізіледі.

Pentium микропроцессорының негізгі ерекшелігі оның микроархитектурасымен байланысты. Микроархитектурасы оның ішкі құрлымының жүзеге асырылуын анықтайды, келетін командалардың орындалу принципін, мәліметтердің орналасу және өңделу тәсілдерін. NetBurst (пакеттік-жеіі) атқа ие болған, Pentium 4 микропроцессорының микроархитектурасы Интернет - қосымшаларымен тиімді жұмыс істеуіне негізделген. Айтып кететін жай, NetBurst микроархитектурасында алдынғы Pentium III модеінде қолданылған көптеген принциптер жүзеге асырылған.

Pentium микропроцессорларының микроархитектурасы

Intel компаниясы AGP шинасымен Pentium II базасы жүйесінде жұмысқа бағдарланған 1740 графикалық процессорын шығарып, графикалық амалдарда өнімділіктің өсу амалын жиілікті ойлауға тырысты. Онда қолданылған жылжымалы нүктелі командалардың параллельді орындалу технологиясы арқасында бұл процессор үшөлшемді графикалық бейнелеудің өңделуі жылдам болуын қамтамасыз етті.

Бұл архитектураның ерекшелігі:

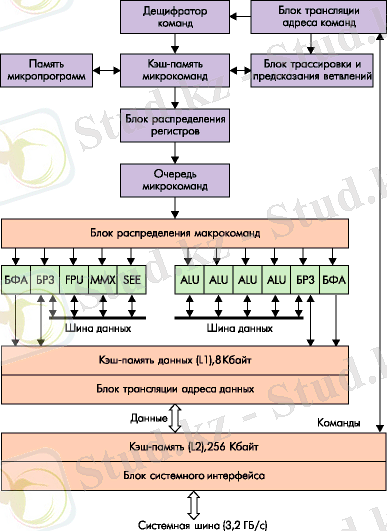

Командалар мен мәліметтер ағыны бөлінген ішкі жадының гарвардтік архитектурасы; Орындаушы құрығыларында параллелді жұмыс істейтін бірнеше командалардың бір уақытта жұмыс істеуін қамтамасыз ететін суперскалярлы архитектура; Тізбекті командаларының динамикалық өзгеруі; Командаларының конвейерлі орындалуы; Pentium 4 микропроцессорының құрылымында бірнеше ерекшеліктері бар (1-сурет) .

Гарвардтік ішкі құрылым жүйелік шинадан келетін сыртқы интерфейс арқылы және процессор кристалында орналасқан ортақ 2-ші деңгейлі сыйымдылығы 256 (512) Кбайт кэш-жады (L2) арқылы, командалардың және мәліметтердің ағымдарының бөліну әдісімен жүзеге асырылады. Бұндай орналасу Pentium III-пен салыстырғанда командалар мен мәліметтердің таңдау уақытын қысқартады, мұндағы кэш-жады бөлек кристалда орналасады, процессормен бірге ортақ корпуста бекітілген. 1-ші деңгейлі кэш-жадының шинасының ені 128 битті құрайды.

Сыртқы интерфейс блогы процессордың жүйелік шинамен ауысуын жүзеге асырады. Оған жады, енгізу/шығару контроллері және басқа жүйенің активті құрылғылары қосылады. Жүйелік шина бойынша ауысу 64-разрядты екі бағытты мәліметтер шинасы, 41-разрядты адрес шинасы көмегімен жүзеге асырылады. Ол 64-байтқа шейін сыртқы жадының таңдау режимдерінің кең спектрде адресацияны қамтамасыз етеді.

1-сурет Pentium 4 микропроцессорының құрылымы

Командалар дешифраторы микропрограммалар жадысымен бірге жұмыс істейді. Келген командалардың орындалуын қамтамасыз ететін, микрокомандалардың тізбегін қалыптастырады. Орындау үшін алынатын, декодталған командалар микрокомандалар кэш-жадысына жүктеледі. Кэш-жады 12000-дай микрокомандалар сақтай алады. Бұл Pentium III - гі кэш-жадыда декодталмаған командалар х86 сақталғаннан маңызды ерекшелігі. Оның тоуынан кейін кез-келген команда декодтаған түрде сақталады. Сондықтан кезекті команда түскенде ізсалу блогы бұл кэш-жадыдан керекті, оның орындалуын қамтамасыз ететін микрокоманданы таңдайды. Егер командалар ағымында шартты өту командасы (программаның тармақталынуы) болса, онда өтудің орындалу шарты анықталғанға дейін келесі таңдалатын команданың адресін қалыптастыратын тармақтауды болжайтын механизм (тетік) қосылады.

Микрокомандаар ағымдарының қалыптасуынан кейін, декодталған командалардың орындалуы үшін қажетті регистрлердің ерекшеленуі өндіріледі. Бұл процедура регистрлер орналастыру блогына кіретін, әрбір белгіленген логикалық регистр командасында 128 физикалық регистрлерден біреуін белгілейтін регистрерді орналастыру блогымен жүзеге асырылады. (Pentium II процессорынде 4 регистер боған) .

Бұл процедура бір уақытта немесе олардың тізбектелінуінің өзгеруімен сол бір логикалық регистрлерді қолданатын командалардың орындалуына рұқсат береді.

Таңдалған микрокомандалар микрокомандалар кезегінде орналасады. Оның ішінде 126-ға дейінгі түскен және декодталған командалардың орындалуын жүзеге асыратын және кейін операндтардың дайын болу шамасына қарай орындау құрылғыларына қарай бағытталған микрокомандалар бар. Айтып кететін жай, Pentium III процессорында кезекте 40 түскен командалар үшін микрокомандалар бар. Кезекте тұрған командалар санының өсуі, параллелді орындала алатын, командалардың орындалу тізбегін өзгерту және командаларды белгілеу арқылы олардың орындалу ағымын тиімді ұйымдастыруын қамтамасыз етеді. Бұл функциялар микрокомандалардың үлестіру блогын жүзеге асырады. Ол микрокомандаарды түсу реті бойынша таңдамайды, ал сәйкес операндтардың және атқару құрылғыларының дайын болуына байланысты таңдайды. Нәтижесінде кейін түскен командалар алдында таңдалған командалардан бұрын орындалуы мүмкін. Сонымен қатар параллелді жұмыс істейтін атқару құрылғыларында бірнеше микрокомандалардың (командалардың) бір уақытта орындалуы болады. Сол себепті параллелді қосылған атқару құрылғыларының толық жүктелуін және процессордың өнімділігін көтеру үшін қамтамасыз ету үшін командалардың кәдімгі орындалу реті бұзылады.

Суперскаляры архитектура параллелді жұмыс істейтін блоктар қатары түрінде процессордың атқару ядросын ұйымдастыру жолымен жүзеге асырылады. Арифметикалық - логикалық блоктар ALU БРЗ берілген регистрерінен келетін, бүтін санды операндтардың өңдеуін жасайды. Бұл регистрлерге операция нәтижесі де енгізіледі. Сонымен қатар шартты өту командалары үшін тармақтану шарты тексеріледі және тармақтануды дұрыс болжамаған кезде командаар конвейерін қайта қосу сигналы беріледі. Атқару ядросы операцияларды орындау үшін жоғарғы жылдамдықпен жұмыс істейді. Мысалы, бүтін санды операндтарды қосу микрокомандасы процессордың тактілік жиілігі 1, 5 МГц болғанда 0, 36 нс ішінде орындалады.

Операндтар адрестері жадыдан таңдалатын, сыйымдылығы 8 Кбайтқа тең 1-ші деңгейлі (L1) кэш-жадымен интерфейсті жүзеге асыратын адресті қалыптастыру блогымен (БФА) есептеледі. Сәйкесінше берілген декодталған командалардағы адрестелу әдістермен БРЗ регистріне жадыдан операндтарды жүктеу үшін 48 адрес және регистрден жадыға жазу үшін 24 адрес қалыптастырылады (Pentium III -те 16 адрес регистрлерді жүктеу үшін және жадыға жазу үшін қалыптастырады) . Сонымен қатар, БФА әлі орындалуға келмеген командаар үшін операндтар адресін қалыптастырады. БФА жадыға қарым - қатынас жасау кезінде бір уақытта 2 операндтың адресін шығарады: біреуі берілген БРЗ регистрге операндты жүктеу үшін, екіншісі нәтижелерді БРЗ -дан жадыға қайта жіберу үшін. Сол себепті, спекулятивті таңдама деп аталатын, атқару блоктарында олардың келесі өңделуі үшін мәліметтерді алдын - ала оқу процедурасы қалыптасады.

Аналогты түрде бөлек жинақ регистрерін және операндтар адресін қалыптастыратын блокты қолданатын SSE, FPU, MMX блоктарының параллелді жұмысы ұйымдастырылады.

Жадыдан операндты таңдау кезінде оқу және жазу бөлек порттар бар кэш-жадыға (L1) қарым - қатынас жасайды. Бір такт ішінде екі команда үшін операндтарды таңдау жүргізіледі. Бұл кэш-жадыға қатынау уақыты тактілік жиілігі 1, 5 ГГц болғанда 1, 42 нс құрайды. Бұл Pentium III салыстырғанда 2, 1 есе кіші. 1-ші деңгейлі кэш-жады процессор жиілігінде жұмыс істейді.

Адрестердің қалыптастырылуы кезінде берілген жады сегментіне қатынас жасалынады. Адрестік кеңестіктің әр жерінде орналасатын, әрбір сегмент беттерге бөліне алады. Адрестерді тарату блоктары беттік жадыны ұйымдастыру кезінде мәліметтер және командалардың физикалық адрестерін қалыптастыруын қамтамасыз етеді. Тарату уақытын қысқарту үшін жиі қолданылатын беттерді базалық адрестерді сақтайтын ішкі буферлі жады қолданылады.

Pentium 4-те командалық орындаудың гиперконвейері технологиясы қолданылады. Бұл кезде конвейердің қадам саны 2-ға тең (Pentium II - 5 Pentium III - 11) . Сол себепті бір уақытта орындалу процесінде 2 команда болуы мүмкін, әр түрлі қадамда жүзеге асырылуы кезінде.

Басқа программа тармақтарынан команданы таңдау және барлық алдынғы қадамдарда тазалауға талап етілген кезде шартты тармақты орындаған кезде оның қайта қосылуы қажеттігінен конвейер тиімділігі тез түседі. Конвейірді қайта қосуға кеткен уақытты қысқарту үшін тармақтануды болжау блогы қолданылады. Оның негізгі бөлігі болып ассоциативті жады болып табылады. Ол адрес тармақталыну буфері деп атаады (BTB - Branch Target Buffer), онда алдында орындалған өтулердің 4092 адресі сақталады. Pentium III-те тек қана өтулердің 512 адресі сақталады. Одан басқа, ВТВ -да тармақтанудың кіріспесін сақтайтын, берілген команданы алдыңғы таңдау кезінде өту болып жатқанын көрсететін биттер бар. Биттер өту командасының неше рет болғанын білдіретін бегісі бар санды сақтайтын 2-битті счетчик ретінде көрсетеді. Кезекті шартты өту командасының түсуі кезінде онда көрсетілген адрес ВТВ құрамымен салыстырылады. Егер ол адрес ВТВ -да жоқ болса, яғни берілген адрес бойынша өтулер формасы, онда тармақтаудың жоқтығы болжанылады. Бұл жағдайда өту командасын ан кейін болатын таңдау және команданы декодтау жалғасады. Белгіленген команданың адрес өтуі ВТВ-да сақталынатын адрестермен сәйкес келсе, онда анализ кіріспесі болады. Анализ процесі кезінде жүзеге асырылып жататын тармақтың бағыты жиі анықталады және де кезектелген өтулер анықталады. Егер тармақтаудың орындалуы болжанылса, онда болжанылған адрес бойынша огрналасқан команда таңдалып конвейерге жүктеледі. Pentium 4-те қолданылатын тармақталуды болжаудың жетілдірілген блогы болжаудың дұрыстығының ықтималдылығын 90%-ке дейін қамтамасыз етеді. Сол себепті конвейердің қайта қосу саны азаяды.

IU1, IU2 блоктары бұл блоктар бүтін санды операцияларды орындайтын командаларды өңдейді. Осы класқа қайта жіберуді орындау командалары, арифметикалық және логикалық операцияларды орындау командалары және басқа да мәліметтерді түрлендіру командалары да кіреді.

FPU блогы жылжымалы нүктелі сандармен операцияларды орындайтын командаларды өңдейді. Бұл класқа жылжымалы нүктелі форматта берілген, нақты, бүтін және екілік-ондық сандармен операцияларды орындайтын командалар кіреді. Бұндай көрсетім өңделетін сандардың диапазонын кеңей туге мүмкіндік береді.

2. Ішкі бүркеме-жады

Бүркеме жады процессор мен негізгі жады арасында орналасқан, шапщаң әрекетті шектеулі көлемді буферлік жады болып табылады. Жұмыс процесінде информацияның бөлек блоктары негізгі жадыдан бүркеме-жадыға көшіріледі. Негізгі жадыдан бүркеме-жадыға ақпаратты жүктеу процедурасы бүркемелеу деп аталады. Процессор командаға немесе мәліметтерге қатынағанда алдымен олардың бүркеме-жадыда бар екенін тексереді. Егер керек ақпарат сол жерде болса, онда ол тез алынады, себебі бүркеме-жадыға қатынау процессордың тактілік жиілігімен орындалады. Қатынаудың осы түрін бүркеме-дәл түсу (кэш-попадание) деп аталады. Егер керек ақпарат бүркеме жадыда болмаса, онда ол негізгі жадыдан алынады және сол сәтте бүркеме-жадыға жазылады. Қатынаудың осы түрін бүркеме-қате түсу (кэш-промах) деп аталады. Адрес

31 12 11 5 4 0

19 255 0

2 - сурет. Бүркеме-жадының құрылымы және оған қатынау блогы.

Егер бүркеме-дәл түсу бүркеме-қате түсуге қарағанда неғұрлым көп жүзеге асырылса, соғұрлым есептеу жүйенің шапшаңдығы өседі.

Р3 процессорарда командаларды және мәліметтерді сақтауға арналған ішкі бүркеме-жады қолданылады. Олардың әрқайсысының көлемі 16 Кбайт.

Ішкі бүркеме жадыдан басқа қосышқа сыртқы бүркеме жады бар. Оған қатынау үшін сыртқы интерфейс блогына қосылатын, процессордің тактілік жиілігімен жұмыс істейтін бөлек шина қолданылады. Бүркеме жадының құрылымы 2-ші суретте көрсетілген. Бұл жады ассоциатифті типті, ұзындығы 32 байт жолдардан тұрады. Командалар бүркеме жадыда жолдар 128 жинаққа біріктірілген S0-S127 және олардың әрқайсысы 4 жолдан (L0, L1, L2, L3) тұрады. Мәліметтердің бүркеме жадысы екі жолы (L0, L1) бар 256 S0-S255 жинақтан тұрады.

Бүркеме жады адрестеуі адрестің 32-разряды көмегімен орындалады, олар үш өріске бөлінеді: TAG, SET, BYTE.

Бүркеме жадыға қатынау негізінде SET өрісінің құрамы таңдалынатын жинақтың номерін анықтайды. Адрестің жоғарғы разрядтарының TAG өрісі, м әндері тектер өрістерінің (TAG0-TAG3) құрамымен таңдалған жинақтың жолдарында салыстырылады. Егер TAG мәні бір жолдың тегінің құрамымен сәйкес келсе, онда бүркеме дәл түсу бекітіліп, BYTE өрісі адрестелген операнд осы жолдан алынады. Егер TAG мәні бір жолдың тегінің құрамымыен сәйкес келмесе, онда бүркеме қате түсу бекітіледі.

Бүркеме жады мен негізгі жады арасында жолдарды қайта жіберуді сыртқы интерфейс блогы дестелі циклдар көмегімен орындайды. Дестелі циклдарды және 64-разрядты жүйелік шинаны қолдану бүркеме жадының құрамын тез жаңартуын қамтамасыз етеді.

1-ші деңгейлі кэш-жады ды өзгеріске ұшырады. Мәліметтерді және командаларды сақтайтын Р3 кэшімен салыстырғанда, Р4-те тек қана 8КБ мәліметтер кэші бар. Процессорге орындалу үшін түсетін командалар Trace Cache атты кэште сақталады. Ол жерде олар декодталған түрде сақталады, яғни процессордың атқаратын құрылғыларына орындалу үшін түсетін, микрооперациялар тізбегі ретінде болады. Бұл кэштің сыйымдылығы 12000 микрооперациялар.

2-ші деңгейлі кэш-жады, Willamette ядросында істелген, 256 КБ көлемімен қалды. L2 кэшінің шина ені 256 бит, бірақ кэш латенділігі 2 есеге түсті. Бұл оның өткізу қабілеттілігін, жиілігі 1, 5 ГГц, 48 ГБ-қа дейін көтерді.

Р3-те қамтамасыз ететін жаңа командалар типі енгізілген:

негізгі жадыға қатынас саны қарастырылуы және қолдану тиімділігінің жоғарылауы мақсатымен мәліметтерді бүркемелеуді басқару; жадымен бірге ауысу және есептеу конвейерінің параллельді жұмыс организация мақсатымен мәліметтерді бүркемелеуді алдын-алу. Жадыдан операндты таңдау кезінде оқу мен жазуға арналған бөлек порттары бар мәліметтер бүркеме-жадысына қатынау орындалады. Нәтижесінде, бір уақытта екі командаға арналған операндтар таңдалады. Мә ліметтер бүркеме-жадыда адрестелетін операнд болмаса буферлік жадыға қа тынау блогы MOB (Memory Order Buffer) көмегімен екінші деңгейлі бүркеме-жадыға немесе негізгі жадыға (жүйелік шина арқылы) қатынау орындалады. Бұл блок операндты орындау кезінде спекулятивтік таңдауды жүзеге асырады.

Негізгі жадыға жазылатын мәліметті аралық сақтау үшін MOB блогының құрамында жазбаның мәліметтер буфері бар.

Сыйымдылығы 32 байт буферлік жады жазба нәтижесін жүйелік шина басқа алмасу циклдерін орындап біткенге дейін кідіртеді.

Процессор жүйелік шинаға қатынауды қажет етпейтін команданы орындығын кезде нәтиже жазылады. Осы арқылы жүйелігінің өнімділігі қосымша өседі.

Бүркеме-жадыны қолдана отырып, негізгі жадымен алмасу дестелі қатынау циклдары арқылы өтеді. Осы циклдар арқылы бүркеме-жадының бір жолдың құрамын (32 байт) қайта жіберуге болады. Сыртқы 64-разрядты мәліметтер шинасы осындай қайта жіберуді машиналық уақыттың бес тактысында орындауға мүмкіндік береді: бірінші такт жолдың адресін орнатуға арналған, ал келесі төрт такт ішінде мәліметтер беріледі. Бұл кезде алмасуды басқаратын керекті сигналдар бір-ақ рет ( циклдың басында) орнатылады, ал беру тактыларындағы адрестің кіші разрядтарының өзгеруі автоматы түрде негізгі жадымен орындалады.

Адрестерді қалыптастыру кезінде берілген жады сегментіне қатынау орындалады. Әр сегмент адрестік кеңестіктің түрлі бөлімдерінде орналасқан парақтарға бөліне алады. Адресті аудару (трансляция) блоктары жадыны парақтық ұйымдастыруды қолданғанда командалар мен мәліметтердің физикалық адрестерін қалыптастыруды қамтамасыз етеді. Бұл кезде аудару уақытын қысқарту үшін ішкі буферлік жады TLB (Translation Look-aside Buffer) қолданылады. Ол жиі қолданылатын парақтардың базалық адресін сақтайды.

Р4 процессорында 12 қадамды командаалр конвейері жүзеге асырылған. Бірінші жеті қадамды өткенде ( ROB блогына дейін) командалардың алғашқы орындалу реті сақталады. Үш атқару қадамдарда командалар реті өзгеруі мүмкін, соңғы екі қадам алынған нәтижелерді жадыға немесе регистрлерге алғашқы орындалу реті қалпына келтіріліп жазылады. Бұндай қалпына келтіруді нәтижелерді жадыға жазғанда, MOB буферлік блогы орындайды. Ал нәтижелер регистрге жазылса (RRF блогына) қалпына келтіруді - орындалу ретін өзгерту блогы және командаларды үлемтіру (ROB және RS) блогы орындайды.

3. Регистрлер

3. 1 Жалпы мақсатты регистрлер

Жалпы мақсатты регистрлер программаларда келесілерді сақтау үшін қолданылады:

Логикалық және арифметикалық операциялардың операндтарын; Адрестің компоненттерін; Жады ұяшықтарына нұсқағыштарды. Осы барлық регитрлердің ішінен esp регистрін жеке айтуға болады. Оны программа операндтарын сақтау үшін қолдануға болмайды. Себебі онда программаның стек төбесіне нұсқағыш сақталады. Осы топтың барлық регитрлері өзінің “кіші” бөліктеріне қатынауға мүмкіндік береді. Өзіндік адрестеу үшін регистрлердің тек кіші 16- және 8-битті бөліктерін қолдануға болады. Бұл регистрлер арифметикалық-логикалық құрылғының (АЛҚ) ішінде орналасқандықтан, оларды АЛҚ регистрлері деп те атайды:

eax/ax/ah/al (Accumulator register) - аккумулятор. Аралық мәліметтерді сақтауға араналған. Кейбір командаларда бұл регистрерді міндетті қолдану керек. ebx/bx/bh/bl (Base register) - базалық регистр. Жадыда кейбір объектінің базалық адресін сақтауға арналған. ecx/cx/ch/cl (Count register) - регистр-санағыш. Кейбір қайталанатын әрекеттерді орындайтын командаларда және сәйкес команданың жұмыс алгоритмінде жасырылған. edx/dx/dh/dl (Data register) - мәліметтер регистрі. eax/ax/ah/al регистрі сияқты аралық мәліметтерді сақтайды. Кейбір командаларда қолдану міндетті, кейбір командаларда бұл айқындалмаған түрде боады. Келесі екі регистр тізбекті операцияларды қолдану үшін қолданылады, яғни ұзындығы 32, 16 немесе 8 бит болып келетін элементтер тізбекшесін тізбекті түрде өңдейді.

esi/si (Source Index register) - түптектің индексі. Бұл регистр түптек-тізбекшедегі элементтердің ағымды адресін қамтиды. edi/di (Destination Index Register) - қабылдауыш индексі. Бұл регистр қабылдауыш-тізбекшедегі элементтердің ағымды адресін қамтиды. Стекпен жұмыс жасау үшін микропроцессордың командалар жүйесінде арнайы командалар бар, ал микропроцессордың программалық моделінде бұл үшін арнайы регистрлер бар.

esp/sp (Stack Pointer register) - стек нұсқағышының регистрі. Ағымдағы стек сигментінде стек төбесінің нұсқағышын қамтиды. ebp/bp (Base Pointer register) - стектің кадр базасының нұсқағыш регистрі. Стек ішіндегі мәліметтерге ерікті қатынауды ұйымдастыру үшін арналған. 3. 2 Сегменттік регистрлер

Микропроцессордың программалық моделінде алты сегменттік регистрлер бар: cs, ss, ds, es, qs, fs. Шағынпроцессор сегменттер деп аталатын үш бөлік түріндегі программаның құрылымдық ұйымдастырылуын қолдайды. Сәйкесінше, жадының осындай ұйымдастырыуы сегменттік деп аталады. Сегменттік регистрлер уақыттың белгілі мезетінде, программа қатынас құра алатын сегменттерге нұсқау үшін арналған.

- Іс жүргізу

- Автоматтандыру, Техника

- Алғашқы әскери дайындық

- Астрономия

- Ауыл шаруашылығы

- Банк ісі

- Бизнесті бағалау

- Биология

- Бухгалтерлік іс

- Валеология

- Ветеринария

- География

- Геология, Геофизика, Геодезия

- Дін

- Ет, сүт, шарап өнімдері

- Жалпы тарих

- Жер кадастрі, Жылжымайтын мүлік

- Журналистика

- Информатика

- Кеден ісі

- Маркетинг

- Математика, Геометрия

- Медицина

- Мемлекеттік басқару

- Менеджмент

- Мұнай, Газ

- Мұрағат ісі

- Мәдениеттану

- ОБЖ (Основы безопасности жизнедеятельности)

- Педагогика

- Полиграфия

- Психология

- Салық

- Саясаттану

- Сақтандыру

- Сертификаттау, стандарттау

- Социология, Демография

- Спорт

- Статистика

- Тілтану, Филология

- Тарихи тұлғалар

- Тау-кен ісі

- Транспорт

- Туризм

- Физика

- Философия

- Халықаралық қатынастар

- Химия

- Экология, Қоршаған ортаны қорғау

- Экономика

- Экономикалық география

- Электротехника

- Қазақстан тарихы

- Қаржы

- Құрылыс

- Құқық, Криминалистика

- Әдебиет

- Өнер, музыка

- Өнеркәсіп, Өндіріс

Қазақ тілінде жазылған рефераттар, курстық жұмыстар, дипломдық жұмыстар бойынша біздің қор #1 болып табылады.

Ақпарат

Қосымша

Email: info@stud.kz