Р6 архитектурасы негізіндегі процессорлардың сипаттамасы мен микроархитектурасы

МАЗМҰНЫ

КІРІСПЕ . . . 3

НЕГІЗГІ БӨЛІМ . . . 4

1 Р6 ҰЙЫМЫ ПРОЦЕССОРЛАРЫНЫҢ СИПАТТАМАСЫ МЕН ЕРЕКШЕЛІКТЕРІ . . . 4

- Архитектура ерекшеліктері . . . 7

- Р6 ұйымы процессорларының түрлері . . . 9

2 Р6 ҰЙЫМЫ ПРОЦЕССОРЛАРЫНЫҢ МИКРОАРХИТЕКТУРАСЫ . . . 17

2. 1 Intel P6 ұйымы процессорларының құрылымы мен жұмыс жасауы . . . 17

2. 2 Pentium II процессорының Fetch/Decode Unit және Dispatch/Execute Unit модулінің блок-схемасы . . . 19

2. 3 Retire Unit және Bus Interface Unit модулі . . . 23

3 ПРОЦЕССОРЛАРДЫҢ ПРИНЦИПИАЛДЫ СҰЛБАСЫ . . . 26

3. 1 Процессорлардың принципиалды сұлбасы . . . 26

ҚОРЫТЫНДЫ . . . 32

ПАЙДАЛАНЫЛҒАН ӘДЕБИЕТТЕР ТІЗІМІ . . . 33

ҚОСЫМША . . . 34

КІРІСПЕ

Процессор немесе микропроцессор компьютердегі орталық мәліметтер өңдеу құрылғысы болып табылады. Процессор микросхема ретінде ұсынылған және оперативті жадымен қатар аналық тақшада орналасады. Процессорлар бағдарламалар жұмысына қажетті есептеулерді орындайды. Процессор неғұрлым шапшаң болса, компьютердің жұмыс істеу жылдамдығы соғұрлым жоғары болады. Процессордың жылдамдығы мегагерцпен (МГц) немесе гигагерцпен (ГГц) өлшенетін оның ырғақтық жиілігімен анықталады. Процессордың үстіне радиатор, радиаторға процессорды салқындатуға арналған желдеткіш (кулер) орнатылады. Әдетте компьютер сипаттамасының басында, орталық процессордың (CPU - central processor unit) типі мен жиілігі, оперативті жады (random access memory, RAM) сипаттамасы беріледі. Компьютердің бұл құрамдас бөліктері - ең бастылары, өйткені олар компьютер жұмысының шапшаңдығын анықтайды.

Процессордың сипаттамасын тактілік жиілігі мен разрядтығы айқындайды. Жұмыс барысында процессор нақты бөлінген уақыт бірлігінде, яғни бір уақыт аралығында - тактте (оқу, жазу, екі санды қосу сияқты) белгілі операцияларды орындайды. Бір тактіге неғұрлым аз уақыт кетсе немесе процессордың тактілік жиілігі жоғары болса, ақпартты өңдеу соғұрлым жылдам болатыны анық.

Процессордың тактілік жиілігі мегагерцпен өлшенеді. 1МГц тактілік жиілік процессордың секундына бір миллион қарапайым операция орындауына парапар. Pentium процессорларының тактілік жиілігі қазір 600 МГц деңгейіне жетеді.

Процессордың өңдеу кезінде оған келіп түскен деректерді сақтауға арналған өзінің ішкі жад ұяшықтары болады. Олар жад регистрлері деп аталады. Процессордың жад регистрлерінде бір байттық, екі байттық немесе сегіз байттық деректер орналасуы мүмкін. Бұл бір байттық регистрі бар процессор немесе оны тағы сегіз разрядты процессор деп те атайды, бір тактіде бір байттық деректі өңдей алатынын білдіреді. Процессордың разряды неғұрлым үлкен болса, компьютер бір тактіде соғұрлым көп ақпарат өңдей алады. Регистрлер машинаның жоғары шапшаңдығын қамтамасыз ету үшін қолданылады.

Микропроцессордың интерфейстік жүйесі процессордың ДК - дің басқа құрылғыларымен байланысын жүзеге асырады.

Р6 ұйымы процессорларының сипаттамасы мен ерекшеліктері

P6 - Intel компаниясымен игерілген және Pentium Pro, Pentium II, Pentium III, Celeron және Xeon микропроцессорларының негізіне кіретін супер скалярлық суперконвейерлі архитектура. Өткен кезеңдегі CISC-ядросы бар x86-үйлесімді процессорлардан P6 архитектурасының процессорларының айырмашылығы, оларда x86-ның күрделі нұсқаулықтарын тікелей атқармайтын, оларды қарапайым ішкі микрооперацияларға кері кодтайтын RISC-ядросы болады.

P6 архитектурасының бірінші процессоры болып жұмыс станциялары және серверлер нарығына бағытталған, 1995 жылдың 1 қарашасында құлағдар етілген Pentium Pro процессоры болды. Pentium Pro процессорлары дербес компьютерлер үшін арналған P5 (Pentium және Pentium MMX) архитектурасының процессорларымен параллель шығарылды. 1997 жылдың 7 мамырында Intel компаниясы P5 архитектурасының процессорларының орнына келген Pentium II процессоры туралы жариялады.

2000 жылы столға қоятын және серверлі процессорлар нарығына P6 архитектурасының орнына NetBurst архитектурасы келді, бірақ P6 архитектурасы Pentium M және Core мобильді процессорларында өз дамуын алды. 2006 жылы NetBurst архитектурасы процессорларының орнына архитектурасы Р6 архитектурасының дамуын ұсынатын Core 2 Duo ұйымының процессорлары келді.

Функционалдық құрылғылар

P6 архитектурасының процессорлары төрті негізгі ішкі жүйелерден тұрады:

• Реттелген алдын ала өңдеулер ішкі жүйесі (англ. In-Order Front End, IOFE) - бағдарламамен ескерілген ретте нұсқаулықтарды іріктеу және қайта кодтау үшін жауап береді және өткелдерді болжайды.

• Өзгертілген тізбектелуі бар орындау өзегі (англ. Out-of-Order Core, O2C) - микрооперациялардың ұтымды ретте орындалуы үшін жауап береді және атқарушы құрылғылардың өзара әрекеттесуін ұйымдастырады.

• Реттеліп аяқталған ішкі жүйе (англ. In-Order Retirement, IOR) - бағдарламамен ескерген ретте орындаулар нәтижелерін беріп отырады.

• Жадтың ішкі жүйесі (англ. memory subsystem) - процессордың жедел жадпен өзара әрекеттесуін қамтамасыз етеді.

Реттелген алдын ала өңдеулер ішкі жүйесі

Бұл ішкі жүйе құрылымдарына мыналар жатады :

• Өткелдерді болжау модулі және буфері (Branch Target Buffer, BTB) - өткелдерді болжайды және өткелдердің тарихи кестесін сақтайды. Болжау үшін динамикалық сияқты статикалық әдістер де қолданылады. Статикалық әдіс, егер динамикалық болжау мүмкін емес болса қолданылады (өткелдер кестесінде қажетті мәлімет жетіспейді) .

• Нұсқаулықтар декодері (Instruction Decoder) - RISC-микрооперацияларынан кейін тізбекті түрде x86 CISC-нұсқаулықтарын өзгертеді. Екі декодер бар: бір микрооперациямен орындалатын командалар өңдеуші қарапайым нұсқаулықтар (Simple) және командаларды өңдеуге бірнеше (төртке дейін) микрооперация қажет болатын күрделі нұсқаулықтар (Complex) .

• Микрооперациялардың тізбектелуін жоспарлауышы (Microcode sequencer) - төрттен көп микрооперацияларды қажет ететін, x86 күрделі нұсқаулықтарды қайта кодтауда қолданылатын микрооперациялардың тізбектелуін сақтайды.

• Келесі нұсқаулықтардың адресін есептеу блогы (Next IP Unit) - үзілістер туралы ақпарат және ауысу кестелері негізінде келесімен өңделуге тиіс нұсқаулықтардың (англ. instruction pointer, IP) адресін есептейді.

• Нұсқаулықтарды іріктеу блогы (Instruction Fetch Unit, IFU) - келесі нұсқаулықтардың адресін есептеу блогымен дайындалған адрес бойынша нұсқаулықтарды жадтан іріктеуді жүзеге асырады.

Tualatin ядросы негізіндегі процессорларында ауысу кестелері негізінде нұсқаулықтарды алдын ала іріктеуді жүзеге асыратын нұсқаулықтарды алдын ала іріктеу ( Prefetcher ) қосымша блогы бар.

Тізбектеп өзгеруі бар орындаулар өзегі

Нәтиже өзгермейтіндей нұсқаманың орындалу реті ауысатын тізбектеп өзгеруі бар орындау сұратулардың оптималды таратуының есебінен жұмысты жеделдетеді. Тізбектеп өзгеруі бар орындауды ұйымдастыратын құрылымдарға мыналар жатады :

• Регистрлерді тағайындау кестесі (Register Alias) - x86/IA32 (Intel Architecture 32-bit) архитектурасының регистрлері арасында және микрооперация орындауда қолданылатын ішкі регистрлері арасында сәйкестік береді.

• Микрооперацияны қайта реттеу буфері (Reorder Buffer) - өнімділік көзқарастан микрооперацияның ұтымды тізбекте орындалуын қамтамасыз етеді.

• Станция-Резервуар (Reservation Station) - атқарушы құрылымдарға жіберілетін нұсқаулықтар бар.

Ядроның атқарушы құрылымдарына мыналар жатады :

• Арифметикалық-логикалық құрылымдар, АЛУ (Arithmetic Logic Unit, ALU) - бүтін санды операцияларды орындайды.

• Жылжымалы үтір бар арифметикалар блогы (Floating Point Unit, FPU) - жылжымалы үтір бар сандарға операциялар орындайды. Pentium III және жоғары процессорларда да SSE (SIMD FPU) нұсқаулығын орындауды жүзеге асыратын блок бар.

• Адресті генерациялау блогы (Address Generation Unit, AGU) - нұсқаулықтармен қолданылатын деректер адресін есептейді және осы деректерді жүктеу/шығару кэшіне сұратуды қалыптастырады

Реттелген аяқтаулар ішкі жүйесі

• Регистрлік файл (Register File) - операциялар нәтижелерін сақтайды (атқарылатын нұсқаулықтар үшін IA32 регистрінің күйі) .

• Жадты қайта реттеу буфері (Memory Reorder Buffer) - нұсқамалардың орындалу ретінің өзгеруі салдарынан қате деректердің жазылуын алдын алу мақсатында жадтағы деректердің жазу ретін басқарады.

• Аяқтау блогы (Retirement Unit) - нұсқамалардың орындалуының нәтижелерін олар орындауға түскен тізбекте береді.

Жадтың ішкі жүйесі

Жадтың ішкі жүйесі жедел жадпен өзара әрекеттесуді жүзеге асырады. Бұл ішкі жүйеге мыналар жатады :

• Деректер үшін бірінші деңгейлі кэш (Level 1 Data Cache, L1D) - аз уақытты 8 (Pentium Pro үшін) немесе 16 килобайт көлеммен рұқсат бар деректерді сақтауға арналған жад.

• Нұсқаулықтар үшін бірінші деңгейлі кэш (Level 1 Instruction Cache, L1I) - аз уақытты 8(Pentium Pro үшін) немесе 16 килобайт көлеммен рұқсат бар жад.

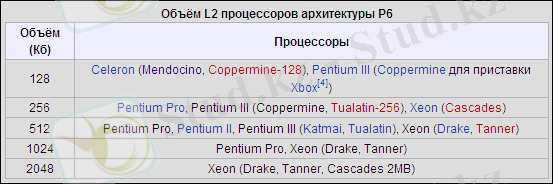

• Екінші деңгейлі кэш (Level 2 Cache, L2) . 128, 256, 512, 1024 немесе 2048 килобайт көлеммен аз уақытты рұқсат бар жад. L2 шинаның ені 64 немесе 256 (Coppermine және жоғары ядродағы прйессорлар үшін) битті құрайды. Covington ядросындағы Celeron процессорларында екінші деңгейлі кэш болмайды.

• Шиналық интерфейс блогы (Bus Interface Unit) - жүйелік шинаны басқарады.

1-сурет. Р6 архитектурасының L2 процессорлар көлемі

Нұсқаулықтардың орындалуы

Нұсқаулықтың орындалуы оның іріктеуінен және қайта кодтаудан басталады. Бұл үшін адрес бойынша бірінші деңгейлі нұсқаулықтың ауысуды болжау беферінен 64 байт (екі жол) таңдалады. Олардан келесі нұсқаулықтың адресін есептеу блогынан бастап 16 байт тегістеледі және x86 нұсқаулықты микрооперацияға түрлендіруші нұсқаулықты қайта кодтаушысына беріледі. Егер нұсқаулықтарға бір микрооперация сәйкес келсе, қайта кодтау қарапайым нұсқаулықтардың бір қайта кодтауын жүргізеді. Егер нұсқаулықтарға екі, үш немесе төрт микрооперация сәйкес келсе, қайта кодтау күрделі нұсқаулықтардың қайта кодталуын жүргізеді. Егер де нұсқаулықтарға микрооперациялардың үлкен саны сәйкес келсе, онда олар микрооперациялардың тізбектелуін жоспарлауышысымен қалыптасады.

Нұсқаулықтарды қайта кодтаудан кейін регистрдің атын өзгерту жүргізіледі, ал микрооперация мен деректер буфер-станцияға орналастырылады, ол жақтан олар сәйкесінше орындаудың ұтымды ретімен және олардың орындалу операндтары үшін қажетті анықтау шарты түрінде атқарушы блоктарға бағытталады (максимум бір такт 5 нұсқаулық) . Орындау микрооперациясының статусы және оның нәтижелері микрооперацияларды қайта реттеу буферінде сақталады.

Микрооперацияларды орындау нәтижелері бойынша олардың орнынан түсуге (англ. Retirement) дайындығы анықталады.

Архитектура ерекшеліктері

P6 архитектурасының алғашқы процессорларының шығарылған сәтте басқа қазіргі процессорлардан едәуір айырмашылығы болды. Pentium Pro процессорының динамикалық орындауы (нұсқалықтың орындалу ретінің өзгеруі), сонымен қатар екі есе тәуелсіз шина архитектурасы (англ. Dual Independent Bus) арқасында негізін салушылар және бәсекелестерге тән жадтың өткізу қабілетіне деген көптеген шектеулердің алынуы. P6 архитектурасының бірінші процессорының тактілік жиілігі 150 МГц құрады, ал бұл архитектураның соңғы өкілдерінің тактілік жиілікті 1, 4 ГГц болды. P6 архитектурасының процессорларының оларға 64 ГБ жадқа дейін (процестің сызықты адрестік кеңістігі 4ГБ дейін шектелген) адрестеуге мүмкіндік беретін 36-разрядты адрес шинасы болды.

Олардың тізбегін өзгертуі бар нұсқаулықтардың орындалуының суперскалярлық тетігі

P6 архитектураларының негізін салушылардан маңызды айырмашылығы x86 нұсқаулықтармен жұмыс істейтін емес, қарапайым ішкі микрооперациялармен жұмыс істейтін RISC-ядросы. Бұл командалардың жүйесіз кодталуы, операндтардың ауыспалы ұзындығы және бүтін санды регистр-жад жіберулердің операцияларысекілді x86 командалар жиынының көптеген шектеулерін алып тастауға мүмкіндік береді.

Суперконвейеризация

P6 архитектурасы поцессорларының 12 кезеңдік тереңдіктегі конвейері бар. Бұл бірдей өндіріс технологиясында өте қысқа конвейері бар процессорлармен салыстырғында өте үлкен тактілік жиілікке жетуге мүмкіндік береді. Осылай, мысалы, AMD K6 процессорлардың ядродағы (конвейердің тереңдігі - 6 кезеңдер, 180 нм. технология) максимал тактілік жиілігі - 550 МГц құрайды, ал Coppermine ядросындағы Pentium III процессорлары 1000 МГц артық.

Нәтижесі шартты ауысулардың орындалу немесе орындалмауына әсер ететін нұсқаулықтар орындауын күту жағдайын болдырмас үшін, P6 архитектурасының процессорларында тарамдаулардың болжауы қолданылады. Бұл үшін P6 архитектурасының процессорларында статикалық және динамикалық болжаулардың сәйкестігі қолданылады: екі деңгейлі адапттивті тарихи алгоритм (англ. Bimodal branch prediction), егер тарамдауларды болжау буферінде ауысудың тарихы болса қолданылады, кері жағдайда статикалық алгоритм қолданылады.

Екі есе тәуелсіз шина

Жад ішкі жүйесінің өткізу қабілеттілігін жоғарылату мақсатпен P6 архитектурасының процессорларында екі есе тәуелсіз шина қолданылады. Бірнеше құрылғыларға жүйелік шинасы ортақ алдыңғы процессорлардан айырмашылығы, P6 архитектурасының процессорларының екі бөлек шинасы бар: процессорды екінші деңгейлі кэш-жадпен жалғастыратын Back side bus, және процессорды микросхема жиынтығының солтүстік көпірімен жалғастыратын Front side bus шиналары.

Артықшылығы

P6 архитектурасының процессорларында негізін салушыларға қарағанда және бәсекелестермен заттық сандарды есептеу жылдамдығында артықшылықтарға жетуге мүмкіндік беретін конвейерленген математикалық сопроцессор (FPU) болады. P6 архитектурасының FPU процессорлары 1999 жылы AMD Athlon процессорлары пайда болғанға дейін бәсекешілердің арасында ең үздік болвп келді.

Сонымен қатар, P6 архитектурасының процессорлары екінші деңгейлі кэш - жадпен жұмыс істеу жылдамдығында және бәсекелестер арасында артықшылықтарға ие болды. Бәсекелес процессорларда (AMD K5, K6, Cyrix 6x86, M-II) өзі қосылатын дәстүрлі жүйелік шина және екінші деңгейлі кэші бар болған уақытта Pentium Pro және Pentium II процессорларында екі есе тәуелсіз шинаналары болды. Екі есе тәуелсіз шинасы бар архитектураны қолданатын Athlon процессорлардың пайда болуымен, өнімділіктегі үзілу қысқартылды, бірақ Pentium III (Coppermine ядросынан бастап) процессорларының 256-разрядты BSB-і 64-разрядты BSB-і бар K7 архитектурасының процессорларына қарағанда екінші деңгейлі кэш-жадпен жылдам жұмыс уақытындағы артықшылықтарды ұстап тұруға мүмкіндік берді. Дегенмен, P6 архитектурасы процессорларының ескірген жүйелік шинасы К7 архитектурасы процессорларының бірінші деңгейлі кэш-жадтың үлкен көлемімен тіркесінде жадтың өткізу қабілетіндегі артықшылықтарға ие болуға мүмкіндік бермеді.

Кемшіліктері

Р6 (Pentium Pro) архитектурасының алғашқы процессорларының ең басты кемшілігі - кең таралған 16-разрядты программалық қамтамасыздандырумен жұмыс кезіндегі төмен өнімділігі. Бұл осындай қосымшалармен жұмыс кезінде нұсқаулықтардың кезектен тыс орындалуының қиын болуымен байланысты болды (мысалы, Pentium Pro процессоры 32-биттік регистрдің оқуын орындай алмайды, егер осыған дейін оның 16-биттік кіші бөлігіне жазба істелінген болса, ал жазбаны орындаған команда кейінге қалдырылған болмаса) . Pentium II процессорында бұл кемшілік дұрысталған, бұл 16-разрядты программалармен жұмыс уақытындағы өнімділіктің үштен бірден көп үлкеюіне алып келді.

P6 архитектурасының процессорларында көп процессорлық жүйелерде жұмыс істеуге мүмкіндік болды, бірақ жүйелік платаға жол салуды ықшамдауға мүмкіндік беретін бөлетін жүйелік шина қолданылды, алайда процессор-жад ішкі жүйелерінің өнімділігіне теріс әсер етті және жүйедегі процессорлардың максимал санына шек қойды.

P6 архитектурасының процессорлары

1-кесте

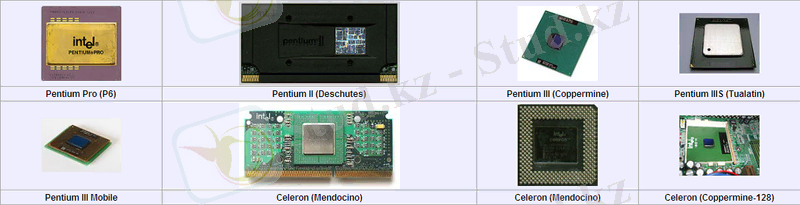

2-сурет. Р6 Процессорларының түрлері

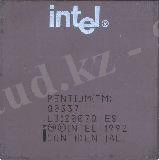

Intel Pentium III (орыс ауыз екі сөйлеуінде - Интел Пентиум три) - 1999 жылдың 26 ақпанында құлағдар етілген Intel P6 архитектурасының x86-үйлесімді микропроцессоры. Pentium III ядросы Deschutes түрлендірілген ядросы негізінде ұсынылып отыр (Pentium II процессорларында қолданылады) . Негізін салушымен салыстырғанда командалардың жиыны (SSE нұсқаулықтарының жиыны қосылған) ұлғайтылған және жадпен жұмыс оптималданған. Бұл SSE кеңейтілуін қолданушы жаңа қосымшалардағы, сол сияқты қазіргі (жадпен жұмыс жылдамдығының өсу есебінен) қолданыстағы қосымшалардағы өнімділікті жоғарылатуға мүмкіндік берді. Сонымен қатар әрбір процессор үшін уникалды қолайлы 64-битті сериялы нөмір енгізілген (3-сурет) .

3-сурет. Intel Pentium III процессоры

Разъёмдары:

- Slot 1

- Socket 370

Ядролар:

- Katmai

- Coppermine

- Tualatin

Орталық процессор (ОП, немесе орталық процессорлық құрылғы ОПҚ central processing unit, қысқаша СPU, толық орталық өңдеуші құрылғы)- электрондық блок немесе микросхема машиналық құрлымдарды орындаушы (програманың кодын )аппараттық қамтамасыз етудің басты бөлімі немесе логикалық компьютердің программалануы, кейде микропроцессор немесе процессор деп атайды.

Алғашында орталық процессорлы құрылғы арнайы логикалық мащиналарды сипаттаған. Қиын програмаларды орындауға арналған сонымен қатар дәл компьютерлік процессорларға арналған, ол тәбиғи жолмен компьютерлерге енгізілген. Терминнің алғашқы қолданылуы және оның аббревиатурасы компьютерлік системағы қатысы 1960 жылдары қойылған. Сол уақыттан бастап процессорлардың құрылысы, архитектурасы бірнеше рет өзгерді, бірақта олардың атқаратын функциясы сол бұрынғыдай болып қалды.

ОПҚ-ның ерекшеліктері такттық желігі, өнімділігі, энергия қолданылуы, қолданбалы техпроцесс(микропроцессорларға арналған)және архитектура.

Алғашқы ОП-лар амбебап құрлымдар түрінде құрылды, олар амбебап және ерекше компьютерлік системавға арналды.

Соңғы жылдары 64 разрядты берілгендер шинасымен жұмыс істейтін Реntium сияқты мол мүмкіндікгі микропроцессорлар да көптеп жарыққа шықты.

Pentium процессоры

Pentium процессоры Intel фирмасының басты жетістіктерінің бірі болды. Pentium процессорын құру 1989 жылғы маусымнан басталды, оны құру және тестілеу процесіне дербес компьютерлер мен программалық жасаудың барлық негізгі құрушылары белсенді қатысты, бұл жобаның жалпы жетістігіне өз ықпалын тигізді. 1991 жылдың соңында процессордың макеті аяқталды, инженерлер онда программалық жасауды іске қоса алды. Жобалау негізінен 1992 жылғы ақпанда аяқталды, процессорлардың тәжірибелі топтамасын тегіс қамтитын тестілеу басталды. 1992 жылғы ақпан айында Pentium процессорының өнеркәсіптік игеруін бастау қажеттігі жөнінде шешім қабылданды, бұл 1993 жылғы 22 наурызда Pentium процессорының кең ауқымды таныстыру рәсімімен аяқталды.

Бір ғана кремний төсемде 3. 1 миллионнан артық транзисторлар біріктірілген 32 разрядты Pentium процессоры жоғары өнімділікпен сипатталады. Pentium процессорының суперскалярлық архитектурасы Intel-мен ғана сәйкес келетін екіконвейрлі индустриалдық архитектураны білдіреді, бұл процессорға тактылық жиіліктің бір кезеңінде бірден астам команданы орындау арқылы өнімділіктің жаңа деңгейіне жетуге мүмкіндік береді. Pentium процессорында құрылған басқа маңызды ревалюциялық жетілдіру, ол жеке бүркемелеуді енгізу. Pentium процессоры жылжымалы үтірлі жетілдірілген құрамдас есептеуіш блогын пайдаланудың арқасында математикалық есептеулерді неғұрлым жоғары деңгейде орындау мүмкіндігін береді. Pentium процессоры сырттан 32-биттық құрылғыны білдіреді. Жадыға деректердің сырт шинасы 64-биттық болып келеді.

Pentium процессоры компьютерлерді «нақты әлемдегі» атрибуттармен жұмыс істеуге үйретті - олар дыбыс, дауыстық және жазба сөйлеу, фотокескіндер.

Pentium Pro процессоры

Процессорлардың алтыншы буынын есептеу 1995 жылғы күзде шығарылған Pentium Pro-дан басталды. Pentium Pro процессорлары олардың бір бөлігі шахматтық тәртіппен орналасқан штырьлік бағыттауыштар матрицасымен SPGA (Staggered Pin Grid Array) модификацияланған корпустарда шығарылды. Бір корпуста (микросхеманың) 2 кристалл орналасқан - процессор ядросы және жеке дайындалған (Intel-дік) екінші реттегі бүркемесі. Бұл бүркеме процессор ядросының жиілігінде жұмыс істеген, бұл Pentium Pro-ның бар тарихында бастапқы 150 МГц-дан небары 200 МГц-ға дейін ғана көтерілді. Түрлі модификациядағы бүркеме көлемі 256 Кбайт-тан 2 Мбайт-қа дейін болды, сенімділікті арттыру үшін ЕСС-бақылау қолданылды. Осы процессорлар үшін 387 бағыттауыштары бар сокет 8 арналған. Интерфейс тікелей симметриялы мультипроцессорлық өңдеу (SMP) үшін 4 процессорға дейін біріктіруге мүмкіндік береді. Функционалдық-артық бақылау (FRC) үшін процессорларды қосарлап қосу мүмкіндігі бар, бұл кезде бір процессор басқасының әрекеттерін тексереді.

Pentium Pro процессоры машина жасау және ғылыми жұмыстарда пайдаланылатын серверлер және жұмыс стансалары, автоматтандырылған жобалау жүйелері, программалық пакеттер үшін 32 разрядты қолданбалардың жылдам әрекетін өсірудің қуатты құралы ретінде құрылды. Барлық Pentium Pro процессорлары жылдам әрекетті одан да көп арттыратын екінші бүркеме-жадымен жарақтандырылады. Аса қуатты Pentium Pro процессоры 5, 5 миллион транзисторларды есепке алады.

ММХ технологиялы процессорлар

1997 жылғы 8 қаңтарда Intel корпорациясы ММХ технологиялы Pentium процессорларымен құлақтандырды - бірінші микропроцессор, онда ақпараттың әр түрлі түрлерімен (бейне, аудио және т. т. ) жұмыс істейтін қолданбалардың тиімділігін арттыруға мүмкіндік беретін Intel құраған жаңа технология іске асырылған.

... жалғасы- Іс жүргізу

- Автоматтандыру, Техника

- Алғашқы әскери дайындық

- Астрономия

- Ауыл шаруашылығы

- Банк ісі

- Бизнесті бағалау

- Биология

- Бухгалтерлік іс

- Валеология

- Ветеринария

- География

- Геология, Геофизика, Геодезия

- Дін

- Ет, сүт, шарап өнімдері

- Жалпы тарих

- Жер кадастрі, Жылжымайтын мүлік

- Журналистика

- Информатика

- Кеден ісі

- Маркетинг

- Математика, Геометрия

- Медицина

- Мемлекеттік басқару

- Менеджмент

- Мұнай, Газ

- Мұрағат ісі

- Мәдениеттану

- ОБЖ (Основы безопасности жизнедеятельности)

- Педагогика

- Полиграфия

- Психология

- Салық

- Саясаттану

- Сақтандыру

- Сертификаттау, стандарттау

- Социология, Демография

- Спорт

- Статистика

- Тілтану, Филология

- Тарихи тұлғалар

- Тау-кен ісі

- Транспорт

- Туризм

- Физика

- Философия

- Халықаралық қатынастар

- Химия

- Экология, Қоршаған ортаны қорғау

- Экономика

- Экономикалық география

- Электротехника

- Қазақстан тарихы

- Қаржы

- Құрылыс

- Құқық, Криминалистика

- Әдебиет

- Өнер, музыка

- Өнеркәсіп, Өндіріс

Қазақ тілінде жазылған рефераттар, курстық жұмыстар, дипломдық жұмыстар бойынша біздің қор #1 болып табылады.

Ақпарат

Қосымша

Email: info@stud.kz